# **CW32L010** Datasheet

## ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ 32-bit low power MCU with up to 64KB FLASH, 4KB RAM

## Rev 1.0

## Important notice - please read carefully

Wuhan Xinyuan Semiconductor Co., Ltd. reserves the right to make changes, corrections, enhancements, and modifications to the product and this document at any time without notice. Buyers should obtain the latest product information on the official website.

Before placing an order for a product, Xinyuan Semiconductor Co. makes a sales acknowledgement in accordance with the terms and conditions of sale at the time of ordering. The purchasers are solely responsible for the selection and usage of Xinyuan Semiconductor company's products, and Xinyuan Semiconductor Co. does not assume any responsibility for the application assistance activities and the design of the purchasers's products. Xinyuan Semiconductor Co. hereby grants no express or implied license to any intellectual property rights. Resale of Xinyuan Semiconductor company's products with provisions that differ from the information described herein will void any warranties granted by Xinyuan Semiconductor Co. with respect to such products.

The CW logo is a trademark of Xinyuan Semiconductor Co.. All other products or service names are the property of their respective owners.

The information in this document supersedes and replaces the information provided in any previous version of this document.

© 2021 Wuhan Xinyuan Semiconductor Co., Ltd. – All rights reserved

www.whxy.com

## Contents

| 1 | Feat                   | ures                |                                                            | . 3 |  |  |  |  |  |

|---|------------------------|---------------------|------------------------------------------------------------|-----|--|--|--|--|--|

| 2 | Intro                  | oductio             | on                                                         | . 5 |  |  |  |  |  |

| 3 | Desc                   | criptio             | ٦                                                          | . 6 |  |  |  |  |  |

| 4 | Fund                   | Functional overview |                                                            |     |  |  |  |  |  |

|   | 4.1                    | ARM® (              | Cortex <sup>®</sup> -M0+ core with embedded Flash and SRAM | 8   |  |  |  |  |  |

|   | 4.2                    | Memo                | ries                                                       | 8   |  |  |  |  |  |

|   | 4.3                    | Boot m              | node                                                       | 9   |  |  |  |  |  |

|   | 4.4                    | Cyclic              | redundancy check calculation unit (CRC)                    | 9   |  |  |  |  |  |

|   | 4.5                    | Power               | management                                                 | 10  |  |  |  |  |  |

|   |                        | 4.5.1               | Power supply schemes                                       | 10  |  |  |  |  |  |

|   |                        | 4.5.2               | Power supply supervisors                                   | 10  |  |  |  |  |  |

|   |                        | 4.5.3               | Voltage regulator                                          | 10  |  |  |  |  |  |

|   |                        | 4.5.4               | Low-power modes                                            | 10  |  |  |  |  |  |

|   | 4.6 Clocks and startup |                     |                                                            |     |  |  |  |  |  |

|   | 4.7                    | Genera              | al-purpose inputs/outputs (GPIO)                           | 12  |  |  |  |  |  |

|   | 4.8                    | Nestec              | vectored interrupt controller (NVIC)                       | 12  |  |  |  |  |  |

|   | 4.9                    | Analog              | ; to digital converter (ADC)                               | 13  |  |  |  |  |  |

|   |                        | 4.9.1               | Temperature sensor                                         | 13  |  |  |  |  |  |

|   |                        | 4.9.2               | Internal voltage reference                                 | 13  |  |  |  |  |  |

|   | 4.10                   | Analog              | voltage comparator (VC)                                    | 14  |  |  |  |  |  |

|   | 4.11                   | Low Vo              | oltage Detector (LVD)                                      | 15  |  |  |  |  |  |

|   | 4.12                   | Timers              | and watchdogs                                              | 16  |  |  |  |  |  |

|   |                        | 4.12.1              | Advanced-control timer (ATIM)                              | 16  |  |  |  |  |  |

|   |                        | 4.12.2              | General-purpose timer (GTIM)                               | 16  |  |  |  |  |  |

|   |                        | 4.12.3              | Low-power timer (LPTIM)                                    | 16  |  |  |  |  |  |

|   |                        | 4.12.4              | Basic timers (BTIM13)                                      | 17  |  |  |  |  |  |

|   |                        | 4.12.5              | Independent watchdog (IWDT)                                | 17  |  |  |  |  |  |

|   |                        | 4.12.6              | SysTick timer                                              | 17  |  |  |  |  |  |

|   | 4.13                   | me clock (RTC)      | 18                                                         |     |  |  |  |  |  |

|   | 4.14                   | Inter-ir            | ntegrated circuit interfaces (I2C)                         | 18  |  |  |  |  |  |

|   | 4.15                   | Univer              | sal asynchronous receiver/transmitter (UART)               | 19  |  |  |  |  |  |

|   | 4.16                   | Serial              | peripheral interface (SPI)                                 | 19  |  |  |  |  |  |

|   | 4.17                   | Infrare             | d modulation transmitter (IR)                              | 19  |  |  |  |  |  |

|   | 4.18                   | Serial              | wire debug port (SWD)                                      | 20  |  |  |  |  |  |

| 5 | Pino                   | descrip             | otions                                                     | 21  |  |  |  |  |  |

| 6 | Add                    | ress m              | apping                                                     | 26  |  |  |  |  |  |

|   |                        |                     |                                                            |     |  |  |  |  |  |

| 7  | Elec | ctrical | characteristics                                        |    |  |

|----|------|---------|--------------------------------------------------------|----|--|

|    | 7.1  | Param   | eter conditions                                        |    |  |

|    |      | 7.1.1   | Minimum and maximum values                             |    |  |

|    |      | 7.1.2   | Typical values                                         |    |  |

|    |      | 7.1.3   | Typical curves                                         |    |  |

|    |      | 7.1.4   | Loading capacitor                                      |    |  |

|    |      | 7.1.5   | Pin input voltage                                      |    |  |

|    |      | 7.1.6   | Power system                                           |    |  |

|    |      | 7.1.7   | Current consumption measurement                        |    |  |

|    | 7.2  | Absolı  | Ite maximum ratings                                    |    |  |

|    | 7.3  | Opera   | ting conditions                                        |    |  |

|    |      | 7.3.1   | General operating conditions                           |    |  |

|    |      | 7.3.2   | Operating conditions at power-up/power-down            |    |  |

|    |      | 7.3.3   | Embedded reset and power control block characteristics |    |  |

|    |      | 7.3.4   | Internal reference voltage                             |    |  |

|    |      | 7.3.5   | Supply current characteristics                         |    |  |

|    |      | 7.3.6   | Wakeup time from low-power mode                        |    |  |

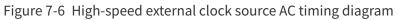

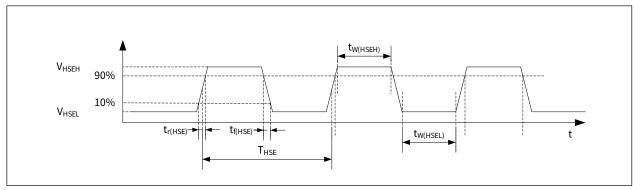

|    |      | 7.3.7   | External clock source characteristics                  |    |  |

|    |      | 7.3.8   | Internal clock source characteristics                  |    |  |

|    |      | 7.3.9   | Memory characteristics                                 |    |  |

|    |      | 7.3.10  | ESD & LU characteristics                               |    |  |

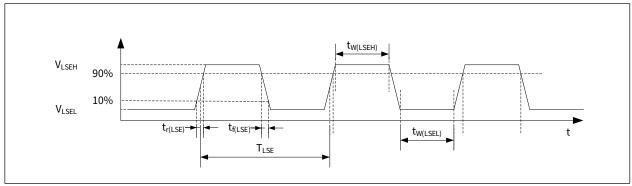

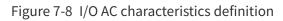

|    |      | 7.3.11  | I/O port characteristics                               |    |  |

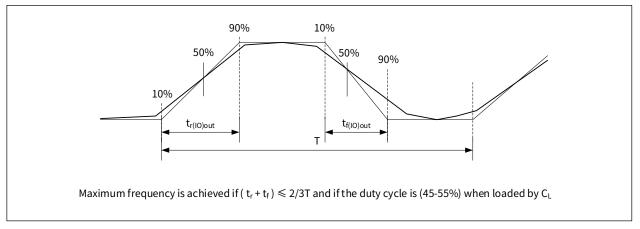

|    |      | 7.3.12  | NRST pin characteristics                               |    |  |

|    |      | 7.3.13  | 12-bit ADC characteristics                             |    |  |

|    |      | 7.3.14  | Temperature sensor characteristics                     |    |  |

|    |      | 7.3.15  | Analog voltage comparator characteristics              |    |  |

|    |      | 7.3.16  | Programmable low voltage detector characteristics      |    |  |

|    |      | 7.3.17  | Timer characteristics                                  |    |  |

|    |      | 7.3.18  | Communication interfaces                               |    |  |

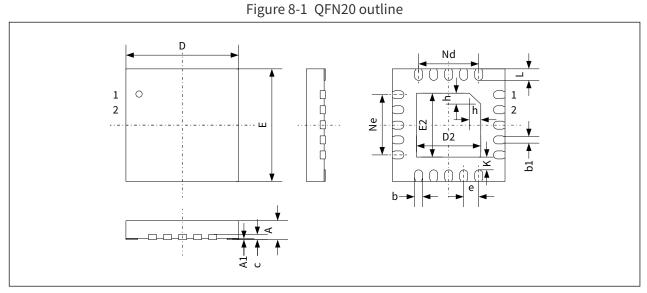

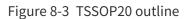

| 8  | Pac  | kage ir | Iformation                                             | 59 |  |

|    | 8.1  | QFN20   | ) package information                                  | 59 |  |

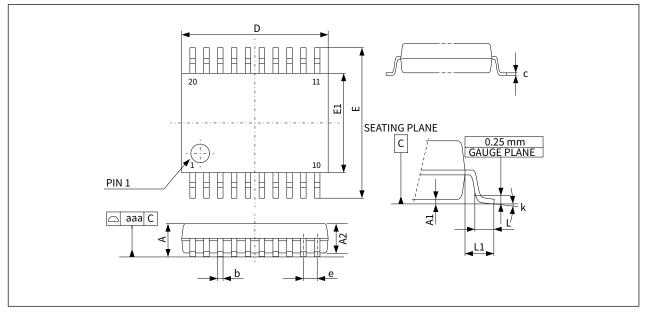

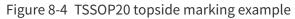

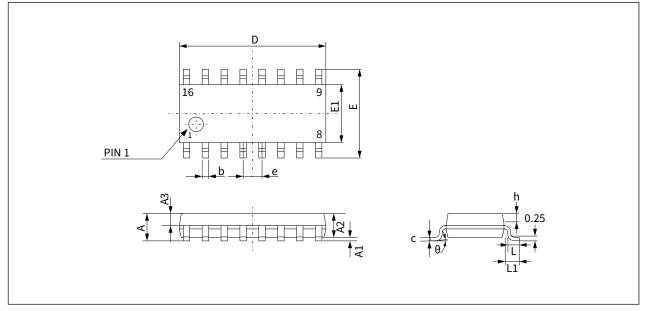

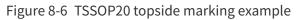

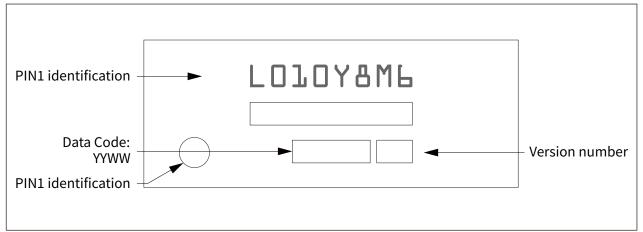

|    | 8.2  | TSSOF   | 20 package information                                 | 61 |  |

|    | 8.3  | SOP16   | package information                                    | 63 |  |

|    | 8.4  |         |                                                        |    |  |

|    |      | 8.4.1   | Reference document                                     |    |  |

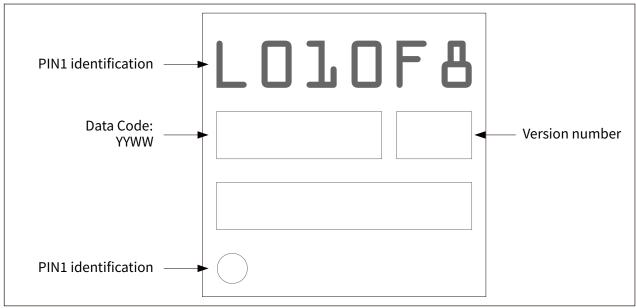

| 9  | Ord  | ering i | nformation                                             |    |  |

| 10 | Rev  | ision h | istory                                                 |    |  |

## 1 Features

- Core: ARM<sup>®</sup> Cortex<sup>®</sup>-M0+

- Frequency up to 48 MHz

- Operating temperature: -40°C to 85°C ; Operating voltage: 1.62V to 5.5V

- Memories

- Maximum 64K bytes FLASH, data retention for 25 years @-40°C  $\sim$  +85°C , support erase protection, read protection and safe runtime protection

- Up to 4K bytes RAM, support hardware parity check

- 22 bytes OTP memory

- CRC calculation unit

- Reset and power management

- Low power modes (Sleep, DeepSleep)

- Power-on/ brown-out reset (POR/BOR)

- Programmable low voltage detector (LVD)

- Clock management

- 4 to 32 MHz crystal oscillator

- 32kHz low speed crystal oscillator

- Internal 48MHz RC oscillator

- Internal 32kHz RC oscillator

- Clock monitoring system

- Allow independent shutdown of each peripheral clock

- Up to 16+1 I/O ports

- All I/O ports support filtered interrupt function.

- All I/O ports support filtered wake-up function.

- All I/O ports support hysteresis and pull-up input.

- All I/O ports support push-pull and open-drain output.

- 12-bit ADC

- Up to 2M SPS conversion speed, sample time for each sequence channel can be configured separately

- 8 conversion result registers

- Built-in 1.2V voltage reference

- Analog watchdog function

- Built-in temperature sensor

- Dual voltage comparator

- Real Time Clock and Calendar

- Support wakeup from Sleep/DeepSleep mode

- Timers

- One 16-bit advanced-control timer, support 6-input capture, support 6 pairs of complementary PWM outputs with dead zone, support two-point comparison, support PWM phase shift

- A group of 16-bit general-purpose timer

- Three groups of 16-bit basic timers

- A group of 16-bit low power timer

- Independent watchdog timer

- Communication interfaces

- Two low-power UARTs, support fractional baud rate, support low-power receive data, support configurable level shifting, one of them supports LIN communication interface.

- One SPI interface 24Mbit/s, support 4~16bit bit width

- One I2C interface 1Mbit/s, supports configurable level shifting, supports SMBUS

- IR modulator, programmable duty cycle and polarity

- Serial wire debug (SWD)

- 80-bit unique ID

#### Table 1-1 Package model list

| Series     | Model      | Package |

|------------|------------|---------|

|            | CW22L010E9 | QFN20   |

| CW32L010x8 | CW32L010F8 | TSSOP20 |

|            | CW32L010Y8 | SOP16   |

## 2 Introduction

This datasheet provides the ordering information and electromechanical characteristics of the CW32L010 microcontrollers.

This document should be read in conjunction with the CW32L010 reference manual.

For information on the Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ core, please refer to the Cortex<sup>®</sup>-M0+ Technical Reference Manual, available from the *www.arm.com*.

## 3 Description

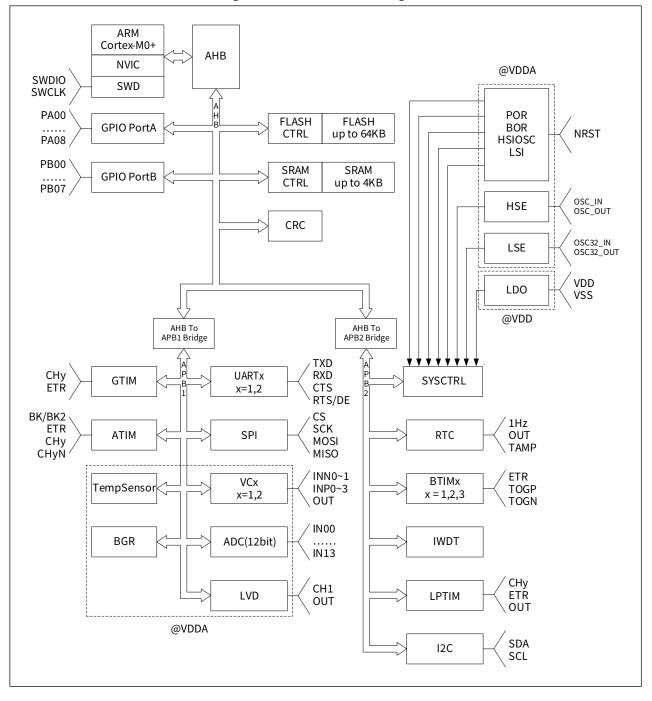

CW32L010 is an eFlash-based single-chip Low-Power microcontroller that integrates an ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core with a main frequency up to 48MHz, high-speed embedded memories(up to 64K bytes of FLASH and up to 4K bytes of SRAM), and an extensive range of enhanced peripherals and I/Os.

All devices offer standard communication interfaces (two UARTs, one SPI, one I2C), one 12-bit ADC, four general-purpose and basic timers, one low-power timer and one advanced-control PWM timer.

CW32L010 operates in the -40°C to 85°C temperature range from a 1.62 to 5.5V power supply, supports two low-power operating modes (Sleep and DeepSleep). The internal block diagram is shown in the following figure:

CW32L010 provides three different packages: QFN20, TSSOP20, SOP16. The functions that can be achieved by products in different packages are different. The details are shown in the following table:

|                      | Peripheral        | CW32L010F8U6 CW32L010F8P6 CW32L010Y |                         |       |  |  |  |

|----------------------|-------------------|-------------------------------------|-------------------------|-------|--|--|--|

| FLASH (              | Kbytes)           | 64                                  |                         |       |  |  |  |

| SRAM (ł              | (bytes)           |                                     | 4                       |       |  |  |  |

|                      | Advanced control  |                                     | 1                       |       |  |  |  |

| Timoro               | General purpose   |                                     | 1                       |       |  |  |  |

| Timers               | Low-power         |                                     | 1                       |       |  |  |  |

|                      | Basic             |                                     | 3                       |       |  |  |  |

| SPI                  |                   | 1                                   |                         |       |  |  |  |

| 12C                  |                   | 1                                   |                         |       |  |  |  |

| UART                 |                   | 2                                   |                         |       |  |  |  |

| 12-bit AD<br>(number | C<br>of channels) | (14 ext.                            | 1<br>(10 ext. + 2 int.) |       |  |  |  |

| GPIO                 |                   | 16                                  | 12+1                    |       |  |  |  |

| Kernel fr            | equency           | 48MHz                               |                         |       |  |  |  |

| Operating voltage    |                   | 1.62V ~ 5.5V                        |                         |       |  |  |  |

| Operatin             | g temperature     | -40°C ~ 85°C                        |                         |       |  |  |  |

| Package              |                   | QFN20                               | TSSOP20                 | SOP16 |  |  |  |

Table 3-1 CW32L010 family device features list

## 4 Functional overview

#### 4.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core with embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ processor is the latest generation 32-bit core for small embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM® Cortex®-M0+ 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an Arm core in the small memory.

The CW32L010 family has an embedded ARM<sup>®</sup> core and is therefore compatible with all ARM<sup>®</sup> tools and software.

#### 4.2 Memories

The device has the following features:

- 4K bytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states and featuring embedded parity checking with exception generation for high reliability critical applications.

- The non-volatile memory is divided into two arrays:

- 64K bytes of embedded Flash memory for programs and data

- 2K bytes of boot program memory

- FLASH memory erasing and reading protection: The FLASH memory erasing and writing protection is performed through the register, and the 4-level read protection level is set through the ISP command.

- LEVELO

No readout protection, the FLASH memory can be read by SWD or ISP.

- LEVEL1

FLASH readout protection, the FLASH memory cannot be read by SWD or ISP. The protection level can be reduced to LEVEL0 through the ISP or SWD interface. After the downgrade, the FLASH is in the whole chip erasing state.

- LEVEL2

FLASH readout protection, the FLASH memory cannot be read by SWD or ISP. The protection level can be reduced to LEVEL0 through the ISP interface. After the downgrade, the FLASH is in the whole chip erasing state.

- LEVEL3

FLASH readout protection, the FLASH memory cannot be read by SWD or ISP. Protection level downgrade in any way is not supported.

## 4.3 Boot mode

The CW32L010 supports the following 2 startup modes:

- Boot from the main FLASH memory and run the user program.

- Boot from bootloader memory and run the internal BootLoader.

When running the Bootloader, the user can use the ISP communication protocol for FALSH programming through UART1 (pins are PA07/PA08). The steps for the CW32L010 to enter ISP mode are as follows:

Step 1: Configure the chip in RESET state;

Step 2: Provide a 50kHz square wave to the chip's UART1\_RXD (SWDIO);

Step 3: Release the chip's RESET state and delay for 5ms;

Step 4: The chip enters ISP mode.

## 4.4 Cyclic redundancy check calculation unit (CRC)

The CRC calculation unit can generate the CRC code of the data stream according to the selected algorithm and parameter configuration.

In some applications, CRC techniques can be utilized to verify the integrity of data transmission and storage.

The product supports eight commonly used CRC algorithms, including:

CRC16\_IBM CRC16\_MAXIM CRC16\_USB CRC16\_MODBUS CRC16\_CCITT CRC16\_CCITT\_FALSE CRC16\_X25 CRC16\_XMODEM

#### 4.5 Power management

#### 4.5.1 Power supply schemes

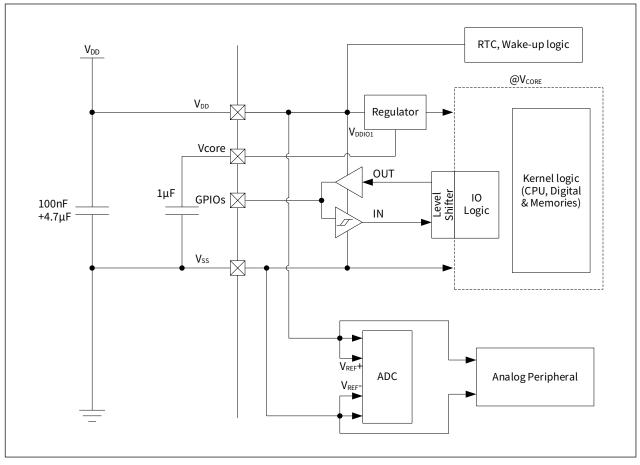

- V<sub>DD</sub> = 1.62V to 5.5V

- Power supply for each digital and analog circuit. Provided externally through VDD pins.

For details about the power supply, refer to *Figure 7-3 Power system*.

#### 4.5.2 Power supply supervisors

The product integrates power-on reset (POR) and brown-out reset (BOR) power monitoring circuits internally, and the power supply is always in an operational state after power-on. The POR/BOR monitors the VDD power supply voltage, and the system enters a reset state when the power supply voltage is monitored to be lower than the reset threshold ( $V_{POR/BOR}$ ). Users do not need to add additional external hardware reset circuit.

#### 4.5.3 Voltage regulator

The internal voltage regulator has "normal" and "low power" operating modes, and it always enabled after reset.

- The "normal" mode corresponds to a state of full speed operation.

- The "low-power" mode corresponds to some power supply working states, including Sleep and DeepSleep working modes.

#### 4.5.4 Low-power modes

The CW32L010 microcontrollers support two low-power modes:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• DeepSleep mode

DeepSleep is used to achieve the lowest power consumption, the CPU stops running, the highspeed clock modules (HSE, HSIOSC) are automatically turned off, and the low-speed clocks (LSE, LSI) remain unchanged.

The device exits DeepSleep mode when an external reset, or an IWDT reset, or some peripheral interrupts, or an RTC event occurs.

#### 4.6 **Clocks and startup**

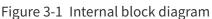

After the MCU is reset, the HSI (generated by the internal 48MHz HSIOSC oscillator frequency division) is selected as the clock source of SysClk by default, and the default value of the system clock frequency is 4MHz.The user can use the program to start the external crystal oscillator and switch the system clock source to the external clock source. The clock failure detection module can continuously detect the state of the external clock source. Once the failure of the external clock source is detected, the system will automatically switch to the internal HSIOSC clock source. If the corresponding fault detection interrupt is enabled, an interrupt will be generated for the user to record fault events.

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

The internal clock tree of the system is shown below :

## 4.7 General-purpose inputs/outputs (GPIO)

Each GPIO pin can be software configured as a push-pull or open-drain digital output, or as a digital input with internal pull-up, as well as peripheral multiplexing.Some GPIO pins have analog functionality and interface with internal analog peripherals.All I/Os can be configured as external interrupt input pins with digital filtering.

## 4.8 Nested vectored interrupt controller (NVIC)

The CW32L010 family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex®-M0+) and supports programmable 4 priority levels.

- Interrupt entry vector table address can be remapped

- Closely coupled NVIC core interface

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

This hardware block provides flexible interrupt management features with minimal interrupt latency.

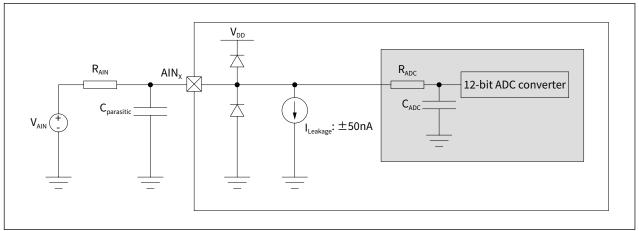

### 4.9 Analog to digital converter (ADC)

The internal 12-bit analog to digital converter has up to 14 external and 2 internal (temperature sensor, BGR 1.2V voltage reference) channels, and support sequence channel conversions mode.

In scan mode, automatic conversion is performed on a selected group of analog inputs.

The analog watchdog function accurately monitors the switching voltage of several selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

#### 4.9.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\text{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN14 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of temperature sensor measurement, manufacturers perform individual factory calibrations for each chip. Temperature sensor factory calibration data is stored in FLASH memory.

| ADC reference voltage | Calibration value storage address | Calibration value accuracy |  |

|-----------------------|-----------------------------------|----------------------------|--|

| V <sub>DD</sub>       | 0x0010 07CE - 0x0010 07CF         | ±3°C                       |  |

Table 4-1 Internal temperature sensor calibration value address

#### 4.9.2 Internal voltage reference

The nominal output voltage of the built-in BGR module of this chip is 1.2V. The voltage output by BGR module of each chip is slightly different. The voltage output by BGR module has been accurately measured and stored in FLASH when it leaves the factory. The voltage value can be read out by using the expression  $*((uint16_t^*) 0x0010 07D2)$ , and its unit is mV.

## 4.10 Analog voltage comparator (VC)

Two analog voltage comparators (VC) are integrated inside, which are used to compare two analog input voltages and output the comparison results from the pins. The positive terminal input of the voltage comparator supports up to 4 external analog inputs, and the negative terminal supports not only 2 external analog inputs, but also internal 1.2V voltage reference and internal resistance voltage divider output voltage. The comparison result output has filtering function, hysteresis window function, and polarity selection. Support compare interrupt, which can be used to wake up MCU in low power mode.

The main features of an analog voltage comparator (VC) are:

- Dual analog voltage comparator VC1、VC2

- Internal 8-step resistor divider

- 4 external analog signal inputs

- 2 on-chip analog input signals

- Built-in Resistor Divider Output Voltage

- Built-in 1.2V reference voltage

- Selectable output polarity

- Support hysteresis window compare function

- Programmable filters and filter times

- 3 interrupt triggering methods, which can be used in combination

- High level trigger

- Rising edge trigger

- Falling edge trigger

- Support running in low power mode, interrupt wake-up MCU

## 4.11 Low Voltage Detector (LVD)

Low Voltage Detector (LVD) is used to monitor the VDD power supply voltage or external pin input voltage. When the comparison results between the monitored voltage and the LVD threshold meets the trigger condition, an LVD interrupt or reset signal will be generated, which is usually used to handle some urgent tasks.

The interrupt and reset flags generated by the LVD can only be cleared by software; only after the interrupt or reset flag is cleared and the trigger condition is reached again, the LVD can generate an interrupt or reset signal again.

The main features of a low voltage detector (LVD) are:

- 2-channel monitoring voltage source: VDD power supply voltage, PA03 pin input

- 8-step threshold voltage, range 1.8V~4.6V

- 3 trigger conditions, which can be used in combination

- Level Triggered: voltage below threshold

- Falling edge trigger: the falling edge when the voltage falls below the threshold

- Rising edge trigger: the rising edge when the voltage rises back above the threshold

- Can trigger to generate interrupt or reset signal, both cannot be generated at the same time

- Programmable filter and filter time

- Support hysteresis function

- Support running in low power mode, interrupt wake-up MCU

## 4.12 Timers and watchdogs

The CW32L010 microcontroller integrates up to 1 general-purpose timer, 3 basic timers, 1 low-power timer and one advanced control timer.

The function differences of timers are shown in the following table:

| Timer<br>type       | Timer | Counter<br>bit width | Counter<br>type      | Prescaler factor        | Capture/<br>compare<br>channels | Complementary<br>outputs |

|---------------------|-------|----------------------|----------------------|-------------------------|---------------------------------|--------------------------|

| Advanced<br>control | ATIM  | 16-bit               | Up, down,<br>up/down | 1,2,3,4,,65536          | 6                               | 6                        |

| General<br>purpose  | GTIM  | 16-bit               | Up, down,<br>up/down | 1,2,3,4,…,65536         | 4                               | 0                        |

| Low power           | LPTIM | 16-bit               | Up, down,<br>up/down | 2 <sup>N</sup> (N=0,,7) | 2                               | 0                        |

|                     | BTIM1 | 16-bit               | Up                   | 1,2,3,4,…,65536         | 0                               | 1                        |

| Basic               | BTIM2 | 16-bit               | Up                   | 1,2,3,4,…,65536         | 0                               | 1                        |

|                     | BTIM3 | 16-bit               | Up                   | 1,2,3,4,…,65536         | 0                               | 1                        |

Table 4-2 Timer feature comparison

#### 4.12.1 Advanced-control timer (ATIM)

The Advanced-control Timer (ATIM) consists of a 16-bit auto-reload counter, driven by a programmable prescaler. ATIM supports timing, counting, reset, gating, trigger and encoder modes, with 6 independent capture/compare channels, enabling 6 independent PWM outputs or 6 pairs of complementary PWM outputs with dead zones or capture of 6 inputs. Can be used for basic timing/counting, measuring pulse width and period of input signals, generating output waveforms (PWM, single pulse, complementary PWM with dead time inserted, etc.).

#### 4.12.2 General-purpose timer (GTIM)

The general purpose timer (GTIM) contains a 16bit auto-reload counter and is driven by a programmable prescaler.GTIM supports various operating modes such as timing, counting, reset, gating, triggering, and encoder, with 4 independent capture/compare channels to measure the pulse width of the input signals (input capture) or to generate output waveforms (output compare and PWM).

#### 4.12.3 Low-power timer (LPTIM)

The internal integration of a 16-bit low power timer (LPTIM) can realize the function of timing or counting external pulses with very low power consumption. By selecting a suitable clock source and trigger signal, it can realize the function of waking up the system when it sleeps with low power consumption. LPTIM has an internal comparison register, which can realize the comparison output and PWM output, and can control the polarity of the output waveform. In addition, LPTIM can be connected with a quadrature encoder to automatically realize counting up and down.

#### 4.12.4 Basic timers (BTIM1..3)

Three basic timers (BTIMs) are integrated internally, each completely independent and functionally identical, each containing a 16-bit automatic reload counter and driven by a programmable prescaler. BTIM supports four working modes: internal counting mode, external counting mode, trigger startup mode and gated counting mode. It supports interrupt when update event and trigger event occur.Counter reset can be controlled by reset input signal under different working modes.

#### 4.12.5 Independent watchdog (IWDT)

Integrated independent watchdog timer (IWDT), once the IWDT is started, the user needs to reload the counter of the IWDT within a specified time interval, otherwise an overflow will trigger a reset or generate an interrupt signal. After the IWDT is started, the counting can be stopped. The user can choose to keep the IWDT running or suspend counting while in DeepSleep mode.

A specially set key-value register can lock the key registers of the IWDT to prevent the registers from being accidentally modified.

#### 4.12.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features are:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

## 4.13 Real-time clock (RTC)

The Real Time Clock (RTC) is a dedicated counter/timer that provides calendar information including hours, minutes, seconds, subseconds, date, month, year, and week day.

RTC has two independent alarm clocks, the time and date can be set in combination, and the alarm clock interrupt can be generated and output through the pin; it supports the time stamp function, which can be triggered by the pin, record the current date and time, and generate a time stamp interrupt at the same time; Support periodic interrupt; support automatic wake-up function, which can generate interrupts and output through pins; support 1Hz square wave and RTCOUT output functions; support internal clock calibration compensation.

The CW32L010 has internal independently calibrated RC clock source with a frequency of 32kHz to provide the drive clock for the RTC. The RTC can run in DeepSleep mode and is suitable for applications requiring low power consumption.

## 4.14 Inter-integrated circuit interfaces (I2C)

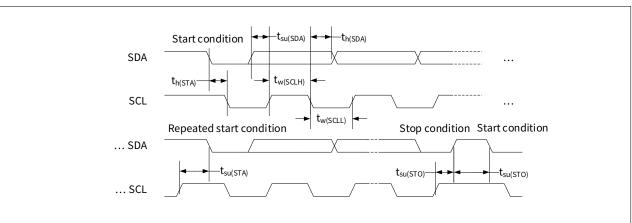

The CW32L010 integrates 1 internal I2C controller, which can serially transmit data to the I2C bus according to the I2C specification at the set transmission rate, and at the same time detect the status during the communication process, and support bus conflict and arbitration processing for multi-master communication.

The main features of the I2C controller are:

- Support master transmit/receive and slave transmit/receive four operating modes

- Support clock stretching (clock synchronization) and multi-master communication conflict arbitration

- Support standard (100Kbps)/fast (400Kbps)/high speed (1Mbps) three operating rates

- Support 7-bit addressing function

- Support 3 slave addresses

- Support broadcast address

- Support input signal noise filtering function

- Support interrupt status query function

- Support SMBUS timeout detection

- Support communication with devices operating at lower voltages than the MCU (via VC)

## 4.15 Universal asynchronous receiver/transmitter (UART)

Internal integration of 2 universal asynchronous receiver/transmitter (UART), supports asynchronous full-duplex, synchronous half-duplex and single-wire half-duplex modes, supports hardware data flow control and multi-machine communication, also supports LIN (Local Interconnect Network); The data frame structure is programmable, and a wide range of baud rate selection can be provided through the fractional baud rate generator. Built-in timer module supports wait timeout detection, receive idle detection, automatic baud rate detection and general timing functions.

The UART controller works in a dual clock domain, allowing data reception in DeepSleep mode, and the reception completion interrupt can wake the MCU back to Active mode.

*Caution: LIN and timer functions are supported for UART1 only; UART2 enables timeout timer related functions by working with slave mode of BTIM/GTIM/ATIM via on-chip peripheral interconnect.*

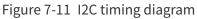

## 4.16 Serial peripheral interface (SPI)

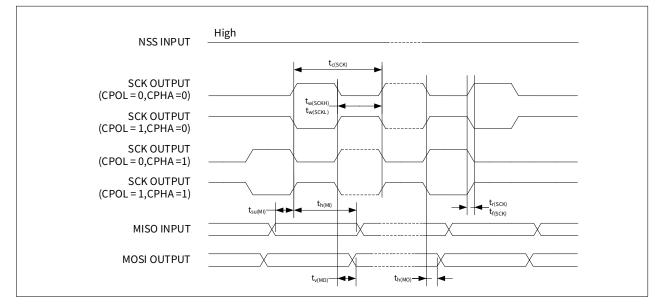

Serial Peripheral Interface (SPI) supports bidirectional full-duplex, single-wire half-duplex and simplex communication modes, MCU can be configured as master or slave, multi-master communication mode is supported.

The main features of the Serial Peripheral Interface (SPI) are the following:

- Support master mode, slave mode

- Support full-duplex, single-wire half-duplex, simplex

- 4-bit to 16-bit selectable data frame width

- Support transmitting and receiving data LSB or MSB first

- Clock polarity and clock phase is programmable

- Communication rates up to PCLK/2 in master mode

- Support multi-machine communication mode

- 8 interrupt sources with flag bits

- Master mode supports interval frame adjustment

- Transmit buffer empty/receive data complete trigger to start ADC

## 4.17 Infrared modulation transmitter (IR)

Internal integrated infrared modulation transmitter (IR), through the timer, UART and IRSW soft control bits with the use of a variety of standard PWM or PPM coding can be easily achieved, can also achieve UART data infrared modulation transmission.

The main characteristics of the infrared modulation transmitter (IR) are the following:

- SIR that supports IrDA standard 1.0

- Maximum data rate of 115.2kbps

- IR emitter tube adaptable to high and low levels

## 4.18 Serial wire debug port (SWD)

An ARM SWD interface is provided, and users can use the CW-DAPLINK of Xinyuan Semiconductor to connect to the MCU to debug and simulate in the IDE development environment.

## 5 Pin descriptions

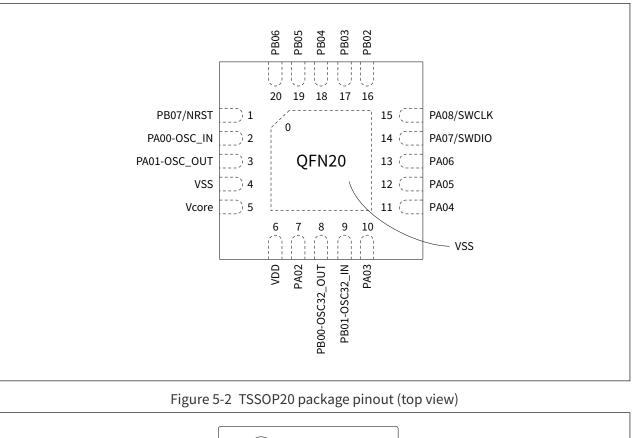

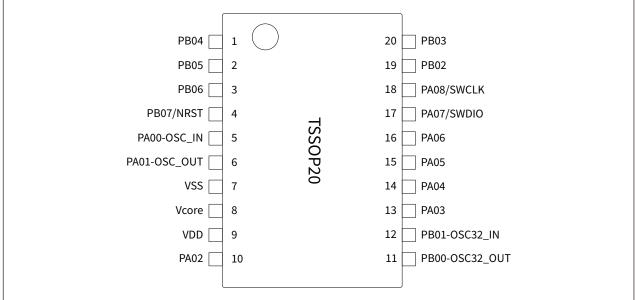

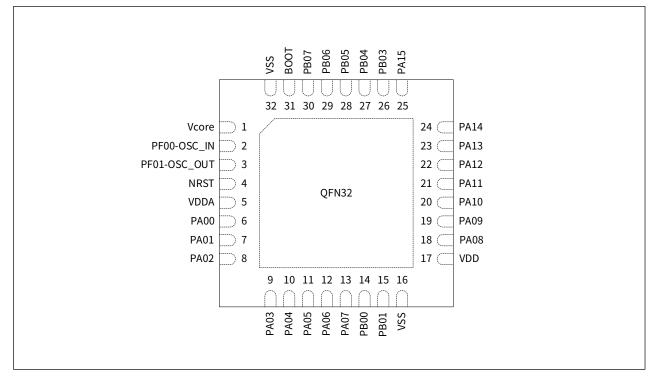

Figure 5-1 QFN20 package pinout (top view)

#### Table 5-1 Legend/abbreviations used in the pinout table

| Name          | Abbreviation                                   | Definition                                                                             |

|---------------|------------------------------------------------|----------------------------------------------------------------------------------------|

| Pin name      | Unless otherwise spe<br>reset is the same as t | ecified in brackets below the pin name, the pin function after<br>the actual pin name. |

|               | S                                              | Supply pin                                                                             |

| Pin type      | I                                              | Input only pin                                                                         |

|               | I/O                                            | Input/output pin                                                                       |

|               | ТТа                                            | Connect the I/O port for the analog function                                           |

| I/O structure | ТС                                             | Standard I/ O pin                                                                      |

|               | RST                                            | Reset input pin                                                                        |

| Notes         | Unless otherwise sp<br>state after reset.      | ecified by a note, all pins are set as high impedance input                            |

| Additional    | Digital function                               | Functions selected through GPIOx_AFRy registers                                        |

| functions     | Analog function                                | Functions directly selected through peripheral registers                               |

| Table 5-2 | CW32L010 pi | n definitions |

|-----------|-------------|---------------|

|-----------|-------------|---------------|

| Pin     | num   | ber   |                                       |        | /O structure |       | Additional functions                                                                          |                                |

|---------|-------|-------|---------------------------------------|--------|--------------|-------|-----------------------------------------------------------------------------------------------|--------------------------------|

| TSSOP20 | QFN20 | SOP16 | Pin name<br>(function<br>after reset) | nction |              | Notes | Digital function                                                                              | Analog<br>function             |

| 1       | 18    | -     | PB04                                  | I/O    | TTa          | _     | UART2_TXD, RTC_OUT, ADC_SAM,<br>BTIM1_ETR, BTIM2_TOGP, GTIM_CH3,<br>ATIM_CH1                  | ADC_IN11,<br>VC2_CH3           |

| 2       | 19    | 1     | PB05                                  | I/O    | ТТа          | -     | UART2_TXD, RTC_TAMP, SPI_MISO,<br>I2C_SDA, GTIM_ETR, GTIM_CH2, ATIM_CH5                       | ADC_IN12,<br>VC1_CH0           |

| 3       | 20    | 2     | PB06                                  | I/O    | TTa          | -     | UART2_RXD, RTC_OUT, SPI_MOSI, I2C_SCL,<br>ATIM_ETR, GTIM_CH1, ATIM_CH5N                       | ADC_IN13,<br>VC2_CH0           |

| 4       | 1     | 3     | PB07/<br>NRST                         | I      | RST          | -     | Default is chip reset input, can also be use<br>(only as input), please refer to SYSCTRL_CR2. |                                |

| 5       | 2     | 4     | PA00                                  | I/O    | ТТа          | _     | UART1_RXD, I2C_SDA, SPI_SCK,<br>BTIM1_TOGP, BTIM3_ETR, ATIM_BK2,<br>ATIM_CH4                  | ADC_IN0,<br>VC1_CH1,<br>OSC_IN |

| 6       | 3     | 5     | PA01                                  | I/O    | ТТа          | -     | UART1_TXD, I2C_SCL, SPI_CS, BTIM1_ ADC_<br>TOGN, GTIM_CH3, ATIM_BK, ATIM_CH4N OSC_            |                                |

| 7       | 4     | 6     | VSS                                   | S      | -            | -     | Ground                                                                                        |                                |

| 8       | 5     | 7     | Vcore                                 | -      | -            | -     | Vcore is the regulator supply output, must b<br>1µF capacitor to ground, and only for interna |                                |

| 9       | 6     | 8     | VDD                                   | S      | -            | -     | Power supply                                                                                  |                                |

| 10      | 7     | -     | PA02                                  | I/O    | ТТа          | -     | PCLK_OUT, SPI_CS, VC1_OUT, IR_OUT,<br>ATIM_ETR, ATIM_CH1N                                     | ADC_IN2                        |

| 11      | 8     | 9     | PB00                                  | I/O    | ТТа          | -     | UART1_RXD, UART2_CTS, SPI_SCK, I2C_<br>SDA, LVD_OUT, BTIM3_TOGP, ATIM_CH1                     | ADC_IN7,<br>OSC32_OUT          |

| 12      | 9     | 10    | PB01                                  | I/O    | ТТа          | -     | UART1_TXD, UART2_RTS, SPI_CS, I2C_<br>SCL, ADC_SAM, BTIM3_TOGN, ATIM_CH2                      | ADC_IN8,<br>OSC32_IN           |

| 13      | 10    | 11    | PA03                                  | I/O    | ТТа          | _     | UART2_TXD, LPTIM_CH1, SPI_MISO,<br>BTIM1_ETR, IR_OUT, GTIM_CH4, ATIM_<br>CH3 LVD_CI           |                                |

| 14      | 11    | 12    | PA04                                  | I/O    | ТТа          | _     | UART2_RXD, LPTIM_CH2, SPI_MOSI,<br>MCO_OUT, VC2_OUT, GTIM_CH3,<br>ATIM_CH1N ADC_IN4           |                                |

| 15      | 12    | 13    | PA05                                  | I/O    | TTa          | -     | UART1_RXD, LPTIM_OUT, SPI_SCK, I2C_ ADC_IN5,<br>SDA, HEXEN, GTIM_CH2, ATIM_CH2N VC2_CH1       |                                |

| 16      | 13    | 14    | PA06                                  | I/O    | ТТа          | -     | UART1_TXD, LPTIM_ETR, SPI_MOSI, I2C_<br>SCL, BTIM2_ETR, GTIM_CH1, ATIM_CH3N                   | ADC_IN6                        |

| Pin     | num   | ber   |                                       |          | Ire           |       | Additional functions                                                           |                      |

|---------|-------|-------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------|----------------------|

| TSSOP20 | QFN20 | SOP16 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Digital function                                                               | Analog<br>function   |

| 17      | 14    | 15    | PA07/<br>SWDIO                        | I/O      | ТС            | 1     | UART1_RXD, I2C_SDA, SPI_MISO,<br>LPTIM_OUT, BTIM2_TOGP, ATIM_BK,<br>ATIM_CH6   |                      |

| 18      | 15    | 16    | PA08/<br>SWCLK                        | I/O      | TC            | 1     | UART1_TXD, I2C_SCL, MCO_OUT,<br>VC1_OUT, BTIM2_TOGN, ATIM_BK2,<br>ATIM_CH6N    |                      |

| 19      | 16    | _     | PB02                                  | I/O      | TTa           | _     | UART2_TXD, UART1_CTS, SPI_MISO,<br>VC2_OUT, LPTIM_CH1, GTIM_ETR,<br>ATIM_CH2   | ADC_IN9,<br>VC2_CH2  |

| 20      | 17    | -     | PB03                                  | I/O      | TTa           | _     | UART2_RXD, UART1_RTS, SPI_MOSI,<br>MCO_OUT, BTIM2_TOGN, GTIM_CH4,<br>ATIM_CH2N | ADC_IN10,<br>VC1_CH3 |

*Caution 1: Afeter reset, these pins are configured as SWDIO and SWCLK functions, and the internal pull-up resistors are turned on by default.*

| Table 5-3 Alternate functions selected t | through GPIOA_AFRy registers |

|------------------------------------------|------------------------------|

|------------------------------------------|------------------------------|

| Pin<br>name | AF1       | AF2       | AF3      | AF4        | AF5        | AF6      | AF7       |

|-------------|-----------|-----------|----------|------------|------------|----------|-----------|

| PA00        | UART1_RXD | I2C_SDA   | SPI_SCK  | BTIM1_TOGP | BTIM3_ETR  | ATIM_BK2 | ATIM_CH4  |

| PA01        | UART1_TXD | I2C_SCL   | SPI_CS   | BTIM1_TOGN | GTIM_CH3   | ATIM_BK  | ATIM_CH4N |

| PA02        | PCLK_OUT  |           | SPI_CS   | VC1_OUT    | IR_OUT     | ATIM_ETR | ATIM_CH1N |

| PA03        | UART2_TXD | LPTIM_CH1 | SPI_MISO | BTIM1_ETR  | IR_OUT     | GTIM_CH4 | ATIM_CH3  |

| PA04        | UART2_RXD | LPTIM_CH2 | SPI_MOSI | MCO_OUT    | VC2_OUT    | GTIM_CH3 | ATIM_CH1N |

| PA05        | UART1_RXD | LPTIM_OUT | SPI_SCK  | I2C_SDA    | HEXEN      | GTIM_CH2 | ATIM_CH2N |

| PA06        | UART1_TXD | LPTIM_ETR | SPI_MOSI | I2C_SCL    | BTIM2_ETR  | GTIM_CH1 | ATIM_CH3N |

| PA07        | UART1_RXD | I2C_SDA   | SPI_MISO | LPTIM_OUT  | BTIM2_TOGP | ATIM_BK  | ATIM_CH6  |

| PA08        | UART1_TXD | I2C_SCL   | MCO_OUT  | VC1_OUT    | BTIM2_TOGN | ATIM_BK2 | ATIM_CH6N |

| Pin<br>name | AF1       | AF2       | AF3      | AF4       | AF5        | AF6        | AF7       |

|-------------|-----------|-----------|----------|-----------|------------|------------|-----------|

| PB00        | UART1_RXD | UART2_CTS | SPI_SCK  | I2C_SDA   | LVD_OUT    | BTIM3_TOGP | ATIM_CH1  |

| PB01        | UART1_TXD | UART2_RTS | SPI_CS   | I2C_SCL   | ADC_SAM    | BTIM3_TOGN | ATIM_CH2  |

| PB02        | UART2_TXD | UART1_CTS | SPI_MISO | VC2_OUT   | LPTIM_CH1  | GTIM_ETR   | ATIM_CH2  |

| PB03        | UART2_RXD | UART1_RTS | SPI_MOSI | MCO_OUT   | BTIM2_TOGN | GTIM_CH4   | ATIM_CH2N |

| PB04        | UART2_TXD | RTC_OUT   | ADC_SAM  | BTIM1_ETR | BTIM2_TOGP | GTIM_CH3   | ATIM_CH1  |

| PB05        | UART2_TXD | RTC_TAMP  | SPI_MISO | I2C_SDA   | GTIM_ETR   | GTIM_CH2   | ATIM_CH5  |

| PB06        | UART2_RXD | RTC_OUT   | SPI_MOSI | I2C_SCL   | ATIM_ETR   | GTIM_CH1   | ATIM_CH5N |

## 6 Address mapping

| 0xFFFF FFFF | RES                          |     |              |                           |            |

|-------------|------------------------------|-----|--------------|---------------------------|------------|

| 0xE0FF FFFF |                              | -   |              |                           |            |

| 0xE000 0000 | M0+ peripherals              |     | 1            | 0x4800 0000-0x4800 03FF   | GPIOA/B    |

| 0XE000 0000 | RES                          |     | AHB -        | 0x4002 3000 - 0x4002 33FF | CRC        |

| 0x4800 17FF | RES                          |     |              | 0x4002 2400-0x4002 27FF   | RAM CTRL   |

|             | AHB                          |     |              | 0x4002 2000 - 0x4002 23FF | FLASH CTRL |

| 0x4002 0000 |                              |     |              | 0x4000 6000-0x4000 7FFF   | LPTIM      |

|             | RES                          |     | APB2<br>APB1 | 0x4000 5800-0x4000 5FFF   | I2C        |

| 0x4000 7FFF | 4.552                        |     |              | 0x4000 5000-0x4000 53FF   | IWDT       |

| 0x4000 4000 | APB2                         |     |              | 0x4000 4800 - 0x4000 4BFF | BTIM1/2/3  |

|             | APB1                         |     |              | 0x4000 4400-0x4000 47FF   | RTC        |

| 0x4000 0000 |                              |     |              | 0x4000 4000-0x4000 43FF   | SYSCTRL    |

|             | RES                          |     |              | 0x4000 1800-0x4000 1BFF   | GTIM       |

| 0x2000 0FFF |                              | - \ |              | 0x4000 1400-0x4000 17FF   | ATIM       |

| 0x2000 0000 | SRAM(4KB)                    |     |              | 0x4000 1000-0x4000 13FF   | UART2      |

| 0,2000 0000 | DEC                          |     |              | 0x4000 0C00 - 0x4000 0FFF | UART1      |

| 0x0010 07FF | RES                          |     |              | 0x4000 0800 - 0x4000 0BFF | SPI        |

| 0x0010 0000 | Boot program<br>memory (2KB) |     |              | 0x4000 0000-0x4000 03FF   | ADC/VC/LVD |

| 0x0000 FFFF | RES                          |     |              |                           |            |

| 0x0000 0000 | FLASH(64KB)                  |     |              |                           |            |

Figure 6-1 CW32L010 internal address mapping

| Device or bus       | Boundary address          | Size | Peripheral     |

|---------------------|---------------------------|------|----------------|

| Main FLASH memory   | 0x0000 0000 - 0x0000 FFFF | 64KB | Main FLASH     |

| Boot program memory | 0x0010 0000 - 0x0010 07FF | 2KB  | BootLoader     |

| OTP memory          | 0x0010 0760 - 0x0010 0775 | 22B  | OTP            |

| SRAM memory         | 0x2000 0000 - 0x2000 0FFF | 4KB  | SRAM           |

|                     | 0x4000 0000 - 0x4000 03FF | 1KB  | ADC/VC/LVD     |

|                     | 0x4000 0800 - 0x4000 0BFF | 1KB  | SPI            |

|                     | 0x4000 0C00 - 0x4000 0FFF | 1KB  | UART1          |

| APB1 peripheral -   | 0x4000 1000 - 0x4000 13FF | 1KB  | UART2          |

| -                   | 0x4000 1400 - 0x4000 17FF | 1KB  | ATIM           |

| -                   | 0x4000 1800 - 0x4000 1BFF | 1KB  | GTIM           |

|                     | 0x4000 4000 - 0x4000 43FF | 1KB  | SYSCTRL        |

| -                   | 0x4000 4400 - 0x4000 47FF | 1KB  | RTC            |

|                     | 0x4000 4800 - 0x4000 4BFF | 1KB  | BTIM123        |

| APB2 peripheral -   | 0x4000 5000 - 0x4000 53FF | 1KB  | IWDT           |

|                     | 0x4000 5800 - 0x4000 5FFF | 1KB  | 12C            |

| -                   | 0x4000 6000 - 0x4000 7FFF | 1KB  | LPTIM          |

|                     | 0x4002 2000 - 0x4002 23FF | 1KB  | FLASH CTRL     |

|                     | 0x4002 2400 - 0x4002 27FF | 1KB  | RAM CTRL       |

| AHB peripheral      | 0x4002 3000 - 0x4002 33FF | 1KB  | CRC            |

| -                   | 0x4800 0000 - 0x4800 03FF | 1KB  | GPIOA/B        |

| M0+ peripheral      | 0xE000 0000 - 0xE00F FFFF | 1MB  | M0+ peripheral |

Table 6-1 CW32L010 peripheral register boundary addresses

## 7 Electrical characteristics

## 7.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to  $V_{\text{ss}}$ .

#### 7.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$ °C and  $T_A = T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\Sigma$ ).

#### 7.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C and  $V_{DD} = 3.3$ V. They are given only as design guidelines and are not tested.

#### 7.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 7.1.4 Loading capacitor

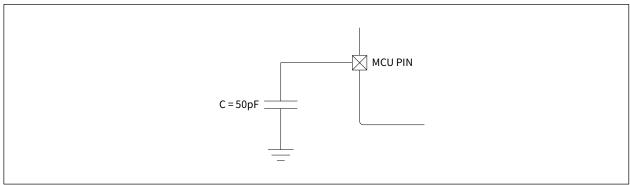

The loading conditions used for pin parameter measurement are shown in the figure below:

Figure 7-1 Pin loading conditions

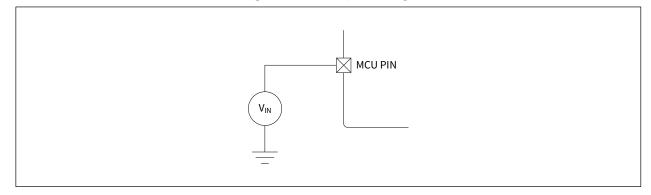

#### 7.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in the figure below:

Figure 7-2 Pin input voltage

#### 7.1.6 Power system

Figure 7-3 Power system

Caution 1: Each power supply pair  $(V_{DD}/V_{SS})$  must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

*Caution 2: All*  $V_{DD}$  *pins must be powered and at the same voltage.*

*Caution 3: Vcore is the regulator supply output and must be connected to a*  $1\mu$ *F capacitor to ground and is for internal circuit use only.*

#### 7.1.7 Current consumption measurement

## 7.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in Table 7-1, Table 7-2 and Table 7-3 may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings Min. Max.                                     |                                                    | Unit |    |

|-----------------------------------|-------------------------------------------------------|----------------------------------------------------|------|----|

| V <sub>DD</sub> - V <sub>SS</sub> | External main supply voltage                          | -0.3 6.0                                           |      | V  |

| V <sub>IN</sub> <sup>2</sup>      | Input voltage on port IO                              | V <sub>SS</sub> -0.3 V <sub>DD</sub> +0.3          |      | V  |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage<br>(human body model) | <i>See Table 7-22 ESD &amp; LU characteristics</i> |      | kV |

Table 7-1 Voltage characteristics<sup>1</sup>

*Caution 1: All main power*  $(V_{DD})$  *and ground*  $(V_{SS})$  *pins must always be connected to the external power supply, in the permitted range.*

Caution 2:  $V_{IN}$  maximum must always be respected, refer to Table 7-2 for the maximum allowable injection current value.

| Symbol                     | Ratings                                                                              | Max. | Unit |

|----------------------------|--------------------------------------------------------------------------------------|------|------|

| I <sub>VDD(PIN)</sub>      | Total current into sum of a single $V_{\mbox{\tiny DD}}$ power lines (source) $^1$   |      |      |

| I <sub>VSS(PIN)</sub>      | Total current out of sum of a single V <sub>ss</sub> power lines (sink) <sup>1</sup> | -100 |      |

|                            | Current into a single I/O or control pin                                             | +25  |      |

| I <sub>IO(PIN)</sub>       | Current out of a single I/O or control pin                                           | -25  |      |

| ΣI                         | Total output current sunk by sum of all I/Os or control pins                         |      | mA   |

| $\Sigma I_{IO(PIN)}$       | Total output current sourced by sum of all I/Os or control pins                      | -80  |      |

| 1 2, 3                     | Injected current on TC and RST pins                                                  | ±5   |      |

| I <sub>INJ(PIN)</sub> 2, 3 | Injected current on TTa pins                                                         | ±5   |      |

| $\Sigma I_{\rm INJ(PIN)}$  | Total injected current (sum of all I/O and control pins) <sup>4</sup>                | ±25  |      |

| Table 7-2 Current characteristics |

|-----------------------------------|

|-----------------------------------|

*Caution 1: All main power* ( $V_{DD}$ ) and ground ( $V_{SS}$ ) pins must always be connected to the external power supply, in the permitted range.

- Caution 2:  $I_{INJ(PIN)}$  must not exceed its limit to ensure that  $V_{IN}$  does not exceed its maximum value. If  $V_{IN}$  cannot be guaranteed to not to exceed its maximum value, also ensure that external limit  $I_{INJ(PIN)}$  is externally limited to not exceed its maximum value. When  $V_{IN} > V_{DD}$ , there is a forward injection current; when  $V_{IN} < V_{SS}$ , there is a reverse injection current.

- *Caution 3: Negative injection disturbs the analog performance of the device.*

- Caution 4: When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents. This result is based on the characterization of the maximum value of  $\Sigma I_{INJ(PIN)}$  on the 4 I/O ports of the device.

| Symbol           | Ratings                      | Value       | Unit |  |

|------------------|------------------------------|-------------|------|--|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |  |

| TJ               | Maximum junction temperature | 105         | °C   |  |

| Table 7-3 | Thermal | characteristics |

|-----------|---------|-----------------|

| Tuble I D | incinia | characteristics |

## 7.3 Operating conditions

#### 7.3.1 General operating conditions

| Table 7 4 | Conserval |           |            |

|-----------|-----------|-----------|------------|

| Table 7-4 | General   | operating | conditions |

| Symbol            | Parameter                                                           | Conditions                                                            | Min. | Max.                 | Unit |  |

|-------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|------|----------------------|------|--|

| f <sub>HCLK</sub> | Internal AHB bus frequency                                          | $V_{DD} \ge 1.8V$                                                     | 0    | 48                   |      |  |

| f <sub>PCLK</sub> | Internal APB bus frequency                                          | $V_{DD} \ge 1.8V$                                                     | 0    | 48                   |      |  |

| f <sub>HCLK</sub> | Internal AHB bus frequency                                          | $1.62 \mathrm{V} \leqslant \mathrm{V}_{\mathrm{DD}} < 1.8 \mathrm{V}$ | 0    | 24                   | MHz  |  |

| f <sub>PCLK</sub> | Internal APB bus frequency                                          | $1.62 \mathrm{V} \leqslant \mathrm{V}_{\mathrm{DD}} < 1.8 \mathrm{V}$ | 0    | 24                   |      |  |

| V <sub>DD</sub>   | Standard operating voltage                                          | -                                                                     | 1.62 | 5.5                  | V    |  |

|                   | I/O input voltage                                                   | TC I/O                                                                | -0.3 | V <sub>DD</sub> +0.3 | V    |  |

| V <sub>IN</sub>   |                                                                     | TTa I/O                                                               | -0.3 | V <sub>DD</sub> +0.3 |      |  |

|                   |                                                                     | TSSOP20                                                               | -    | 263                  |      |  |

| P <sub>D</sub>    | Power dissipation at $T_A = 85^{\circ}$ C for suffix 6 <sup>1</sup> | QFN20                                                                 | -    | 220                  | mW   |  |

|                   |                                                                     | SOP16                                                                 | -    | 500                  |      |  |

| т                 | Ambient temperature                                                 | Maximum power dissipation                                             | -40  | 85                   | - °C |  |

| T <sub>A</sub>    | (suffix 6 version)                                                  | Low power dissipation <sup>2</sup>                                    | -40  | 105                  |      |  |

| TJ                | Junction temperature range                                          | Suffix 6 version                                                      | -40  | 105                  | °C   |  |

Caution 1: If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (See 8.7 Thermal characteristics).

*Caution 2: In low power dissipation state, T*<sub>A</sub> *can be extended to this range as long as T*<sub>J</sub> *does not exceed T*<sub>Jmax</sub> (See 8.7 Thermal characteristics).

#### 7.3.2 Operating conditions at power-up/power-down

The parameters given in the table below are tested under the working conditions listed in *Table 7-4 General operating conditions*.

| Symbol           | Parameter                      | Conditions | Min. | Max.  | Unit |

|------------------|--------------------------------|------------|------|-------|------|

| +                | $V_{\text{DD}}$ rise time rate |            | 0    | 10000 |      |

| t <sub>vdd</sub> | $V_{DD}$ fall time rate        | -          | 20   | 10000 | μs/V |

Table 7-5 Operating conditions at power-up/power-down

#### 7.3.3 Embedded reset and power control block characteristics

The parameters given in the table below are tested under the working conditions listed in *Table 7-4 General operating conditions*.

|  | Symbol                             | Parameter                             | Conditions   | Min.              | Тур. | Max.              | Unit |

|--|------------------------------------|---------------------------------------|--------------|-------------------|------|-------------------|------|

|  | V <sub>por/bor</sub>               | Power on/brown-out<br>reset threshold | Falling edge | 1.45 <sup>1</sup> | 1.50 | 1.55 <sup>2</sup> | V    |

|  |                                    |                                       | Rising edge  | 1.50 <sup>2</sup> | 1.55 | 1.60              | V    |

|  | $V_{\rm BORhyst}$ <sup>3</sup>     | BOR hysteresis                        | -            | -                 | 50   | -                 | mV   |

|  | t <sub>RSTTEMPO</sub> <sup>3</sup> | Reset temporization                   | -            | 4                 | 6.5  | 18                | ms   |

Table 7-6 Embedded reset and power control block characteristics

*Caution 1: The product behavior is guaranteed by design down to the minimum V*<sub>POR/BOR</sub> value. *Caution 2: Data based on characterization results, not tested in production. Caution 3: Guaranteed by design, not tested in production.*

#### 7.3.4 Internal reference voltage

| Table 7-7 | Internal | reference voltage |

|-----------|----------|-------------------|

|-----------|----------|-------------------|

| Symbol                 | Parameter                       | Conditions                     | Min. | Тур.             | Max. | Unit   |

|------------------------|---------------------------------|--------------------------------|------|------------------|------|--------|

| V <sub>REFINT1V2</sub> | Internal 1.2V reference voltage | -40°C < T <sub>A</sub> < +85°C | -    | 1.2 <sup>2</sup> | -    | V      |

| $T_{Coeff}^{1}$        | Temperature coefficient         | _                              | -40  | -                | +40  | ppm/°C |

| t <sub>setup</sub>     | Set-up time                     | -                              | -    | 45               | -    | μs     |

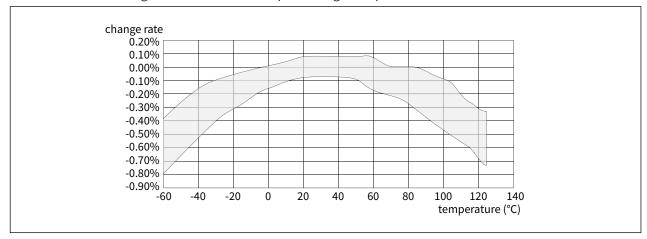

*Caution 1: Guaranteed by design, not tested in production. The range of measured voltage data change rate of multiple chips is shown in the shaded part of the figure below.*

*Caution 2: The actual value of the internal 1.2V reference voltage of each chip is stored in FLASH, see ADC chapter of 'user manual' for details.*

Figure 7-5 BGR 1.2V output voltage temperature characteristics

#### 7.3.5 Supply current characteristics

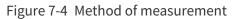

Current consumption is affected by many factors, such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

*Figure 7-4 Method of measurement* shows the circuit for testing current consumption.

All result of the Run-mode current consumption measurements based on the same limited code used to test CoreMark.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency :

- 0 wait state inserted when 0 to 24MHz

- 1 wait state inserted when above 24MHz

- 2 wait state inserted when above 48MHz

- When the peripherals are enabled  $f_{PCLK} = f_{HCLK}$

The data given in Table 7-8 to Table 7-11 are derived from tests performed under the ambient temperature and supply voltage noted in the remarks. For the test conditions, see *Table 7-4 General operating conditions*.

|                 | Parameter                                                                | Conditions          | f <sub>HCLK</sub> | All peripherals<br>enabled |                     | All peripherals<br>disabled |                       |      |

|-----------------|--------------------------------------------------------------------------|---------------------|-------------------|----------------------------|---------------------|-----------------------------|-----------------------|------|

| Symbol          |                                                                          |                     |                   | Тур.                       | Max. <sup>1</sup>   | Typ.                        | Max. <sup>1</sup>     | Unit |

|                 |                                                                          |                     |                   |                            | $T_A = 85^{\circ}C$ |                             | T <sub>A</sub> = 85°C |      |

|                 | Supply current<br>in Active mode,<br>(code executing<br>from Flash)      | HSI or HSE<br>clock | 48MHz             | 4.2                        | 4.85                | 2.7                         | 3.1                   |      |

|                 |                                                                          |                     | 24MHz             | 2.9                        | 3.2                 | 2.1                         | 2.3                   |      |

| I <sub>DD</sub> |                                                                          |                     | 12MHz             | 2.0                        | 2.2                 | 1.85                        | 1.95                  |      |

|                 |                                                                          |                     | 8MHz              | 1.92                       | 2.15                | 1.7                         | 1.8                   |      |

|                 |                                                                          |                     | 4MHz              | 1.30                       | 1.37                | 1.18                        | 1.15                  |      |

|                 | Supply current<br>in Active mode<br>(code executing<br>from RAM)         | HSI or HSE<br>clock | 48MHz             | 3.7                        | 4.72                | 2.1                         | 2.93                  |      |

|                 |                                                                          |                     | 24MHz             | 2.0                        | 2.63                | 1.25                        | 1.73                  | mA   |

| I <sub>DD</sub> |                                                                          |                     | 8MHz              | 0.9                        | 1.2                 | 0.65                        | 0.93                  |      |

|                 |                                                                          |                     | 4MHz              | 0.65                       | 0.83                | 0.51                        | 0.71                  |      |

|                 | Supply current in<br>Sleep mode (code<br>executing from<br>Flash or RAM) | HSI or HSE<br>clock | 48MHz             | 2.38                       | 2.9                 | 0.86                        | 1.2                   |      |

|                 |                                                                          |                     | 24MHz             | 1.40                       | 1.73                | 0.62                        | 0.85                  |      |

| I <sub>DD</sub> |                                                                          |                     | 8MHz              | 0.71                       | 0.93                | 0.45                        | 0.6                   |      |

|                 |                                                                          |                     | 4MHz              | 0.54                       | 0.72                | 0.41                        | 0.58                  |      |

Table 7-8 Typical and maximum current consumption

Caution 1: Data based on characterization results, not tested in production unless otherwise specified.

| Symbol             | Daramatar                                                                                                               | Conditions                |                        | V <sub>DD</sub> = 1.62V~5.5V |                   | V <sub>DD</sub> = 3.3V | Unit |

|--------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------|------------------------------|-------------------|------------------------|------|

| Symbol             | Parameter                                                                                                               | Conditions                | )                      | Min. <sup>1</sup>            | Max. <sup>1</sup> | Тур.                   | Unit |

|                    | Supply current                                                                                                          |                           | T <sub>A</sub> = -40°C | 69                           | 81                | 73                     |      |

|                    | in Active mode<br>(code executing<br>from FLASH, all<br>peripheral clocks<br>enabled)<br>I <sub>DD</sub> Supply current | LSE=32768Hz<br>(DRIVER=0) | T <sub>A</sub> = 25°C  | 72                           | 85                | 76                     |      |

|                    |                                                                                                                         |                           | $T_A = 50^{\circ}C$    | 74                           | 90                | 78                     |      |

|                    |                                                                                                                         |                           | T <sub>A</sub> = 85°C  | 81                           | 102               | 85                     |      |

| I <sub>DD</sub>    |                                                                                                                         |                           | T <sub>A</sub> = -40°C | 67                           | 79                | 71                     | μA   |

|                    | in Active mode<br>(code executing                                                                                       | LSE=32768Hz               | T <sub>A</sub> = 25°C  | 71                           | 84                | 75                     |      |

| from FL<br>periphe | from FLASH, all                                                                                                         | (DRIVER=0)                | $T_A = 50^{\circ}C$    | 73                           | 89                | 77                     |      |

|                    | peripheral clocks<br>disabled)                                                                                          |                           | T <sub>A</sub> = 85°C  | 79                           | 101               | 84                     |      |

Table 7-9 Current consumption when system clock is LSE

*Caution 1: Data based on characterization results, not tested in production unless otherwise specified.* Table 7-10 Typical and maximum current consumption in DeepSleep

| Symbol         | Daramatar                                                    | Conditions                                               | Typ. @V <sub>DD</sub> | Max. <sup>1</sup>    | Unit |  |

|----------------|--------------------------------------------------------------|----------------------------------------------------------|-----------------------|----------------------|------|--|

| Symbol         | Parameter                                                    | Conditions                                               | 3.3V                  | T <sub>A</sub> =85°C | Unit |  |

|                | Supply current in                                            | The regulator is in Active mode, all oscillators are off | 0.3                   | 1.5                  |      |  |

| DeepSleep mode | The regulator is in Active mode,<br>LSE, RTC and IWDT are on | 1.2                                                      | 2.75                  | μΑ                   |      |  |

Caution 1: Data based on characterization results, not tested in production unless otherwise specified.

#### Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = 3.3V

- All I/O pins are in analog input configuration

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency:

- 0 wait state inserted when 0 to 24MHz

- 1 wait state inserted when above 24MHz

- 2 wait state inserted when above 48MHz

- When the peripherals are enabled,  $f_{PCLK} = f_{HCLK}$

#### Table 7-11 Typical current consumption in Active mode, program running from FLASH

|                 |                |                                    |                   | Ту                     |                         |      |

|-----------------|----------------|------------------------------------|-------------------|------------------------|-------------------------|------|

| Symbol          | Parameter      | Conditions                         | f <sub>нськ</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit |

|                 |                | ply current<br>ctive mode<br>clock | 48MHz             | 4.2                    | 2.7                     |      |

|                 |                |                                    | 24MHz             | 2.9                    | 2.1                     |      |

| I <sub>DD</sub> | Supply current |                                    | 12MHz             | 2.0                    | 1.85                    | mA   |

|                 | in Active mode |                                    | 8MHz              | 1.92                   | 1.7                     |      |

|                 |                |                                    | 4MHz              | 1.30                   | 1.18                    |      |

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

• I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up resistors values given in *Table 7-23 I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.