# CW32L031 Reference Manual

ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ Low-power 32-bit MCU

Rev 1.0

www.whxy.com

# Statement

# Important notice

This reference manual is aimed at application developers and provides complete information on how to use the CW32L031 microcontroller memory and peripherals. This operation applies only to CW32L031 devices.

#### Disclaimer

Wuhan Xinyuan Semiconductor Co., Ltd. reserves the right to make changes, corrections, enhancements, and modifications to the product and this document at any time without notice. Buyers should obtain the latest product information on the official website.

# Copyright statement

The copyright of this manual belongs to Wuhan Xinyuan Semiconductor Co., LTD., and we reserve the right of final interpretation and modification of this manual and statement.

# **Technical support**

If you have any comments or suggestions in the process of using, please feel free to contact us.

| Websit :   | www.whxy.com                                                              |

|------------|---------------------------------------------------------------------------|

| Address :  | 5 WuDaYuan 3rd Road, Donghu High-tech Development Zone Wuhan Hubei, China |

| Postcode : | 430070                                                                    |

# Contents

| Sta | temer | nt        |                                                             | 1  |

|-----|-------|-----------|-------------------------------------------------------------|----|

| 1   | Docu  | mentat    | ion conventions                                             | 21 |

|     | 1.1   | Typogr    | raphical conventions                                        |    |

|     | 1.2   | Registe   | er protocol                                                 | 22 |

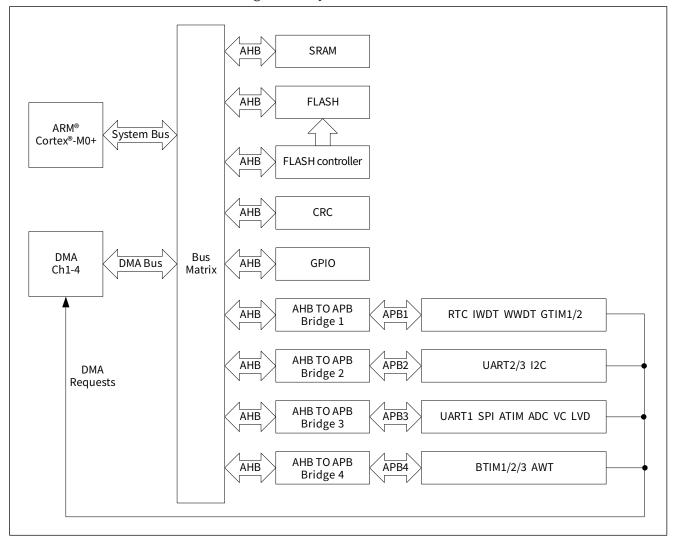

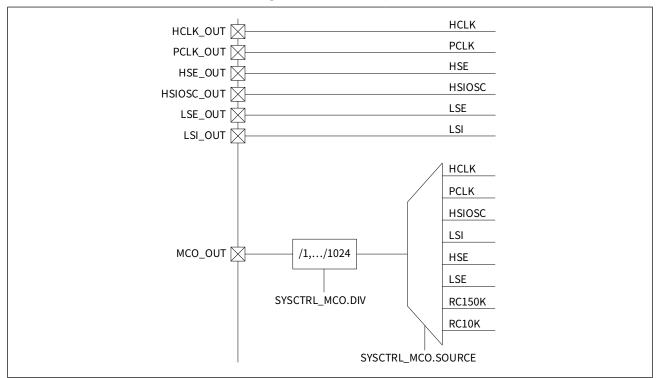

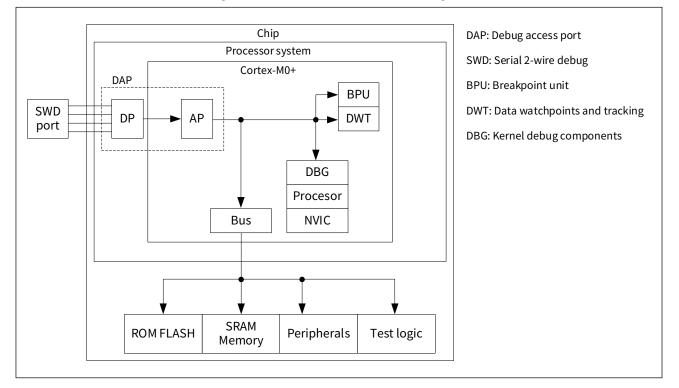

| 2   | Syste | em and i  | memory overview                                             | 23 |

|     | 2.1   | System    | n architecture                                              | 23 |

|     | 2.2   | Memor     | ry organization                                             |    |

|     |       | 2.2.1     | Overview                                                    | 25 |

|     |       | 2.2.2     | Memory map and register boundary addresses                  | 26 |

|     | 2.3   | On-chi    | p SRAM memory                                               | 27 |

|     | 2.4   | On-chi    | p FLASH memory                                              |    |

|     | 2.5   | One-ti    | me programmable OTP memory                                  | 29 |

|     | 2.6   |           | n boot configuration                                        |    |

|     | 2.7   | -         | itions                                                      |    |

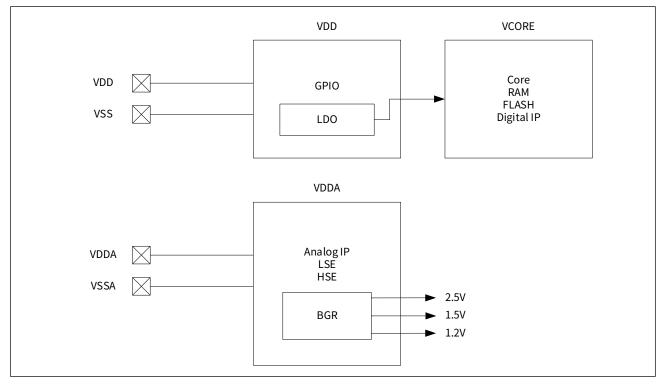

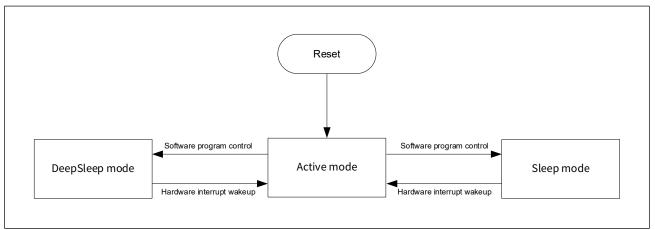

| 3   | Powe  |           | ol (PWR) and Power Consumption                              |    |

|     | 3.1   |           | ew                                                          |    |

|     | 3.2   |           | supply supervisor                                           |    |

|     | 3.3   |           | ing mode                                                    |    |

|     | 0.0   | 3.3.1     | Entering Sleep mode or DeepSleep mode                       |    |

|     |       | 3.3.2     | Exiting Sleep mode or DeepSleep mode                        |    |

|     |       | 3.3.3     | Operating Modes and Reset Sources                           |    |

|     | 3.4   | Low-po    | ower consumption applied                                    | 39 |

|     | 3.5   |           | <sup>®</sup> -M0+ kernel system control register (SCB->SCR) |    |

| 4   | Reset | t and clo | ock control (RCC)                                           | 41 |

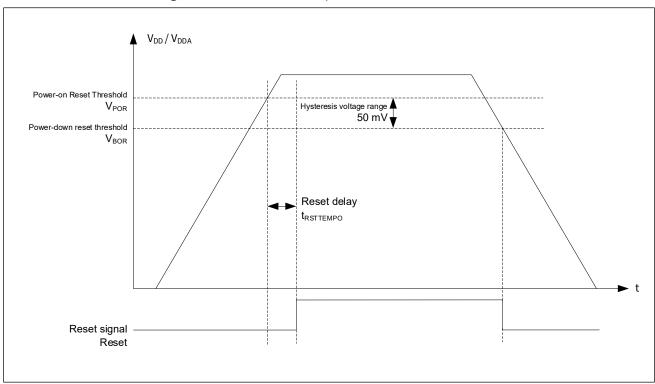

|     | 4.1   |           | n reset                                                     |    |

|     |       | 4.1.1     | Power on reset/Brown-out reset (POR/BOR)                    |    |

|     |       | 4.1.2     | Pin input reset (NRST)                                      |    |

|     |       | 4.1.3     | IWDT/WWDT reset                                             | 42 |

|     |       | 4.1.4     | LVD low voltage detection reset                             | 42 |

|     |       | 4.1.5     | Kernel SYSRESETREQ reset                                    | 42 |

|     |       | 4.1.6     | Kernel LOCKUP fault reset                                   | 42 |

|     | 4.2   | Periph    | eral reset                                                  | 43 |

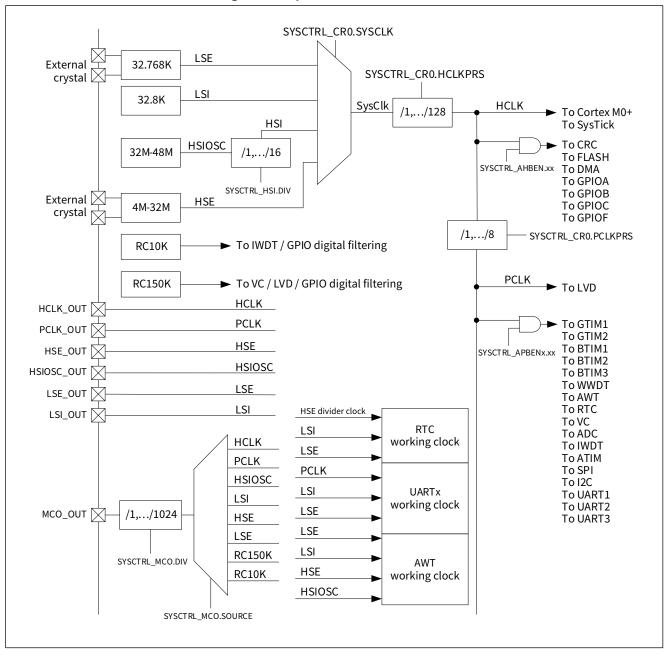

|     | 4.3   | Clock a   | and Control                                                 | 44 |

|     |       | 4.3.1     | Overview                                                    | 44 |

|     | 4.3.2   | System Clock and Operating Mode                               | 46 |

|-----|---------|---------------------------------------------------------------|----|

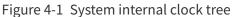

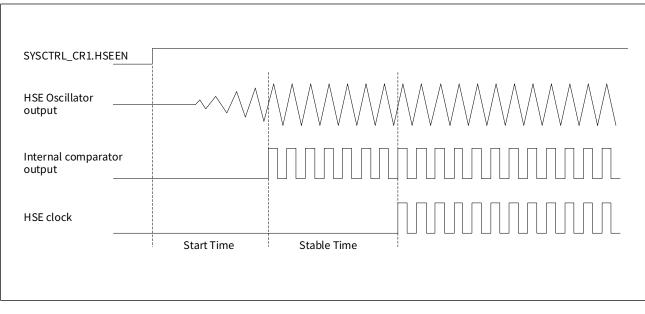

|     | 4.3.3   | HSE clock                                                     | 47 |

|     | 4.3.4   | HSIOSC clock                                                  | 49 |

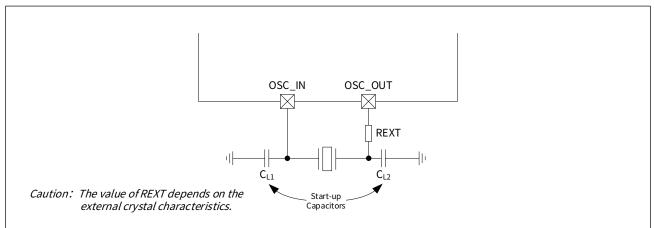

|     | 4.3.5   | LSE clock                                                     | 50 |

|     | 4.3.6   | LSI clock                                                     | 52 |

|     | 4.3.7   | SysClk system clock                                           | 52 |

|     | 4.3.8   | On-chip peripheral clock control                              | 53 |

| 4.4 | Clock S | Start, Calibration, and Status Detection                      | 54 |

|     | 4.4.1   | Clock start                                                   | 54 |

|     | 4.4.2   | Clock calibration                                             | 55 |

|     | 4.4.3   | Clock state detection                                         | 56 |

|     |         | 4.4.3.1 Clock stability detection                             | 56 |

|     |         | 4.4.3.2 Clock start-up failure detection                      | 57 |

|     |         | 4.4.3.3 In-flight failure detection of clocks                 | 58 |

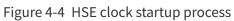

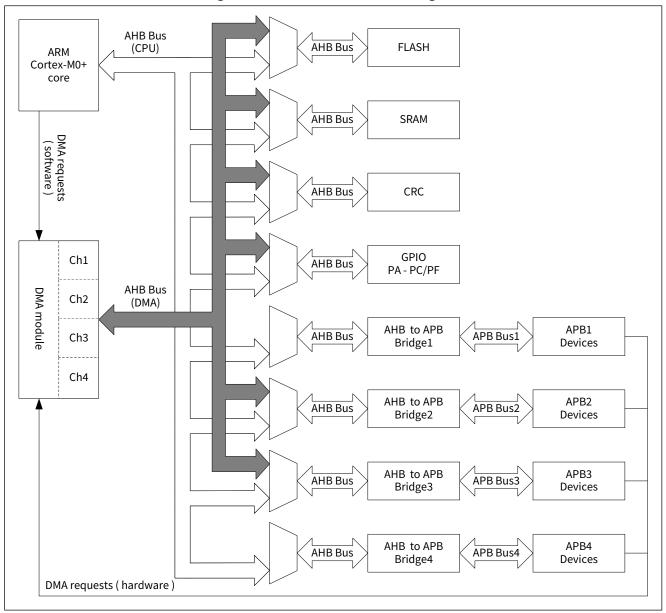

|     | 4.4.4   | Clock verification and output                                 | 59 |

| 4.5 | SysClk  | system clock switch                                           | 60 |

|     | 4.5.1   | Standard Clock Switching Process                              | 61 |

|     | 4.5.2   | HSI clock switching process between different frequencies     | 62 |

|     | 4.5.3   | Example of switching from other clocks to LSE                 | 62 |

|     | 4.5.4   | Example of switching from other clocks to HSE                 | 63 |

|     | 4.5.5   | Example of switching from other clocks to LSI                 | 63 |

|     | 4.5.6   | Example of switching from other clocks to HSI                 | 64 |

| 4.6 | List of | registers                                                     | 65 |

| 4.7 | Registe | er description                                                | 66 |

|     | 4.7.1   | SYSCTRL_CR0 System Control Register 0                         | 66 |

|     | 4.7.2   | SYSCTRL_CR1 System Control Register 1                         | 67 |

|     | 4.7.3   | SYSCTRL_CR2 SYSCTRL_CR2 System Control Register 2             | 69 |

|     | 4.7.4   | SYSCTRL_HSI Internal high frequency clock control register    | 70 |

|     | 4.7.5   | SYSCTRL_LSI Internal low frequency clock control register     | 71 |

|     | 4.7.6   | SYSCTRL_HSE External high frequency crystal control register  | 72 |

|     | 4.7.7   | SYSCTRL_LSE External low frequency crystal control register   | 74 |

|     | 4.7.8   | SYSCTRL_IER System Interrupt Enable Control Register          | 75 |

|     | 4.7.9   | SYSCTRL_ISR System Interrupt Flag Register                    | 76 |

|     | 4.7.10  | SYSCTRL_ICR System Interrupt Flag Clear Register              | 77 |

|     | 4.7.11  | SYSCTRL_AHBEN AHB Peripheral Clock Enable Control Register    | 78 |

|     | 4.7.12  | SYSCTRL_APBEN1 APB Peripheral Clock Enable Control Register 1 | 79 |

|     | 4.7.13  | SYSCTRL_APBEN2 APB Peripheral Clock Enable Control Register 2 | 80 |

|     | 4.7.14  | SYSCTRL_AHBRST AHB Peripheral Reset Control Register          | 81 |

|     | 4.7.15  | SYSCTRL_APBRST1 APB Peripheral Reset Control Register 1       | 82 |

|   |       | 4.7.16        | SYSCTRL_APBRST2 APB Peripheral Reset Control Register 2                           | 83           |

|---|-------|---------------|-----------------------------------------------------------------------------------|--------------|

|   |       | 4.7.17        | SYSCTRL_RESETFLAG System Reset Flag Register                                      | 84           |

|   |       | 4.7.18        | SYSCTRL_DEBUG Debug Status Timer Control Register                                 | 85           |

|   |       | 4.7.19        | SYSCTRL_GTIM1CAP General-Purpose Timer 1 Input Capture Source Configu<br>Register | ration<br>86 |

|   |       | 4.7.20        | SYSCTRL_GTIM2CAP General-Purpose Timer 2 Input Capture Source Configu<br>Register |              |

|   |       | 4.7.21        | SYSCTRL_ATIMETR Advanced Timer ETR Source Configuration                           | 87           |

|   |       | 4.7.22        | SYSCTRL_GTIMETR General Purpose Timer ETR Source Configuration Register           | 88           |

|   |       | 4.7.23        | SYSCTRL_TIMITR Timer ITR Source Configuration Register                            | 89           |

|   |       | 4.7.24        | SYSCTRL_MCO System Clock Output Control Register                                  | 90           |

| 5 | Inter | r <b>rupt</b> |                                                                                   | 91           |

|   | 5.1   | Overv         | iew                                                                               | 91           |

|   | 5.2   | Main f        | eatures                                                                           | 91           |

|   | 5.3   |               | upt priority                                                                      |              |

|   | 5.4   | Interru       | upt vector table                                                                  | 92           |

|   | 5.5   | Interru       | upt related registers                                                             | 94           |

|   |       | 5.5.1         | NVIC interrupt enable and disable enable                                          |              |

|   |       | 5.5.2         | NVIC interrupt pending and clear pending                                          |              |

|   |       | 5.5.3         | NVIC interrupt priority                                                           |              |

|   |       | 5.5.4         | NVIC interrupt mask                                                               | 95           |

|   |       | 5.5.5         | Peripheral interrupt enable                                                       | 95           |

|   | 5.6   | List of       | registers                                                                         | 96           |

|   | 5.7   | Regist        | er description                                                                    | 97           |

|   |       | 5.7.1         | NVIC_ISER Interrupt Enable Setting Register                                       |              |

|   |       | 5.7.2         | NVIC_ICER Interrupt Enable Clear Register                                         |              |

|   |       | 5.7.3         | NVIC_ISPR Interrupt Pending Setup Register                                        | 97           |

|   |       | 5.7.4         | NVIC_ICPR Interrupt Pending Clear Register                                        | 98           |

|   |       | 5.7.5         | NVIC_IPR0 Interrupt Priority Control Register 0                                   | 98           |

|   |       | 5.7.6         | NVIC_IPR1 Interrupt Priority Control Register 1                                   | 99           |

|   |       | 5.7.7         | NVIC_IPR2 Interrupt Priority Control Register 2                                   | 99           |

|   |       | 5.7.8         | NVIC_IPR3 Interrupt Priority Control Register 3                                   | 100          |

|   |       | 5.7.9         | NVIC_IPR4 Interrupt Priority Control Register 4                                   | 100          |

|   |       | 5.7.10        | NVIC_IPR5 Interrupt Priority Control Register 5                                   | 101          |

|   |       | 5.7.11        | NVIC_IPR6 Interrupt Priority Control Register 6                                   | 101          |

|   |       | 5.7.12        | NVIC_IPR7 Interrupt Priority Control Register 7                                   | 102          |

| 6 | RAM   | Memor         | y                                                                                 | 103          |

|   | 6.1   | Overv         | iew                                                                               | 103          |

|   | 6.2   | Main f        | eatures                                                                           | 103          |

|   | 6.3  | RAM          | Memory operation                          |     |  |

|---|------|--------------|-------------------------------------------|-----|--|

|   |      | 6.3.1        | Read operation                            |     |  |

|   |      | 6.3.2        | Write operation                           |     |  |

|   | 6.4  | Parity       | check function                            |     |  |

|   | 6.5  | List o       | f registers                               |     |  |

|   | 6.6  | Regist       | ter description                           |     |  |

|   |      | 6.6.1        | RAM_ADDR Parity Error Address Register    |     |  |

|   |      | 6.6.2        | RAM_IER Interrupt Enable Control Register |     |  |

|   |      | 6.6.3        | RAM_ISR Interrupt Flag Register           |     |  |

|   |      | 6.6.4        | RAM_ICR Interrupt Flag Clear Register     |     |  |

| 7 | FLAS | FLASH Memory |                                           |     |  |

|   | 7.1  | Overv        | <i>v</i> iew                              |     |  |

|   | 7.2  | Main         | features                                  |     |  |

|   | 7.3  | FLASH        | H Memory organization                     |     |  |

|   | 7.4  |              | H memory read wait cycle configuration    |     |  |

|   | 7.5  |              | H Memory operation                        |     |  |

|   |      | 7.5.1        | Page Erase                                |     |  |

|   |      | 7.5.2        | Write operation                           |     |  |

|   |      | 7.5.3        | Read operation                            |     |  |

|   | 7.6  | FLASH        | H Memory protection                       |     |  |

|   |      | 7.6.1        | Erase and write protection                |     |  |

|   |      | 7.6.2        | Erase and write PC page protection        |     |  |

|   |      | 7.6.3        | Read protection                           |     |  |

|   |      | 7.6.4        | FLASH memory programming                  |     |  |

|   | 7.7  | Preca        | utions                                    |     |  |

|   | 7.8  | List o       | f registers                               |     |  |

|   | 7.9  |              | ter description                           |     |  |

|   |      | 7.9.1        | FLASH_CR1 Control register 1              |     |  |

|   |      | 7.9.2        | FLASH_CR2 Control register 2              | 122 |  |

|   |      | 7.9.3        | FLASH_PAGELOCK Erase lock register        |     |  |

|   |      | 7.9.4        | FLASH_IER Interrupt Enable Register       |     |  |

|   |      | 7.9.5        | FLASH_ISR Interrupt Flag Register         |     |  |

|   |      | 7.9.6        | FLASH_ICR Interrupt Flag Clear Register   |     |  |

| 8 | Dire | ct mem       | ory access (DMA)                          | 125 |  |

|   | 8.1  | Overv        | /iew                                      |     |  |

|   | 8.2  | Main         | features                                  | 125 |  |

|   | 8.3  | Funct        | ional block diagram                       |     |  |

| Contents | С | 0 | n | t | e | n | ts |  |

|----------|---|---|---|---|---|---|----|--|

|----------|---|---|---|---|---|---|----|--|

|   | 8.4  | DMA t   | ransfer modes                                                | 128 |

|---|------|---------|--------------------------------------------------------------|-----|

|   |      | 8.4.1   | Overview of Transfer Modes                                   | 128 |

|   |      | 8.4.2   | Software trigger BLOCK transfer mode                         | 130 |

|   |      | 8.4.3   | Software trigger BULK transfer mode                          |     |

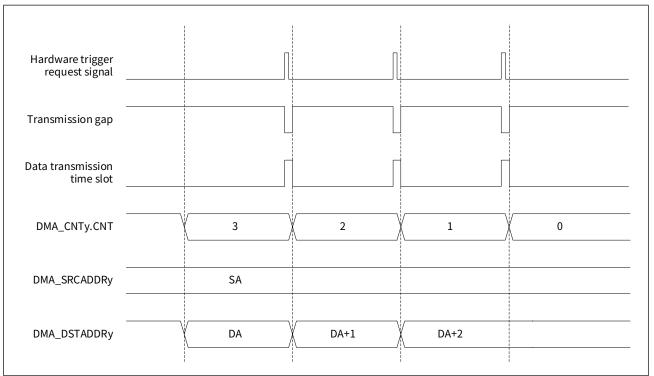

|   |      | 8.4.4   | Hardware trigger BLOCK transfer mode                         |     |

|   |      | 8.4.5   | Hardware trigger BULK transfer mode                          |     |

|   | 8.5  | Other   | <sup>r</sup> configuration of DMA                            |     |

|   |      | 8.5.1   | Data width                                                   |     |

|   |      | 8.5.2   | Data block size                                              |     |

|   |      | 8.5.3   | Number of data blocks                                        |     |

|   |      | 8.5.4   | Channel priority                                             |     |

|   | 8.6  | DMA i   | 135                                                          |     |

|   | 8.7  | List of | f registers                                                  | 136 |

|   | 8.8  | Regist  | ter description                                              | 137 |

|   |      | 8.8.1   | DMA_ISR Interrupt Flag Register                              |     |

|   |      | 8.8.2   | DMA_ICR Interrupt Flag Clear Register                        |     |

|   |      | 8.8.3   | DMA_CSRy Channel y Control and Status Register               |     |

|   |      | 8.8.4   | DMA_TRIGy channel y trigger suorce control register          |     |

|   |      | 8.8.5   | DMA_CNTy Channel y transfer number register                  |     |

|   |      | 8.8.6   | DMA_SRCADDRy Channel y transfer source address register      |     |

|   |      | 8.8.7   | DMA_DSTADDRy Channel y transfer destination address register |     |

| 9 | Gene | eral-pu | rpose input/output (GPIO)                                    |     |

|   | 9.1  | Overv   | /iew                                                         |     |

|   | 9.2  | Main    |                                                              |     |

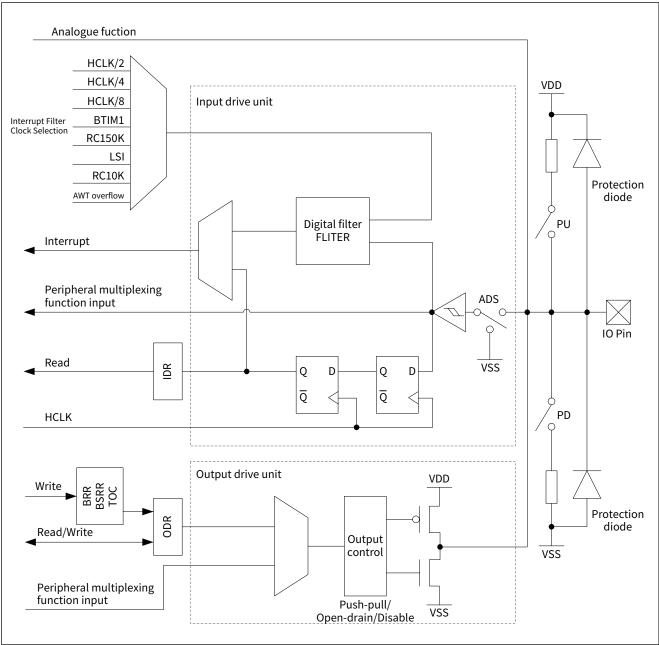

|   | 9.3  | Funct   | ion description                                              | 143 |

|   |      | 9.3.1   | Functional block diagram                                     |     |

|   |      | 9.3.2   | Digital output                                               |     |

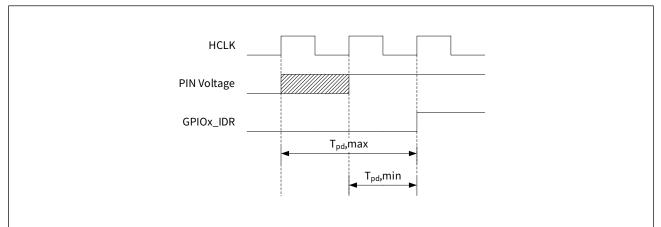

|   |      | 9.3.3   | Digital input                                                |     |

|   |      | 9.3.4   | Analogue function                                            |     |

|   |      | 9.3.5   | Multiplexing function                                        |     |

|   |      | 9.3.6   | Interrupt Function                                           |     |

|   |      | 9.3.7   | Other functions                                              |     |

|   | 9.4  | Progr   | amming example                                               | 150 |

|   |      | 9.4.1   | Digital output programming example                           | 150 |

|   |      | 9.4.2   | Digital input programming example                            | 150 |

|   |      | 9.4.3   | Analog functional programming example                        | 150 |

|   |      | 9.4.4   | Multiplexed function programming example                     | 150 |

|   |      | 9.4.5   | Interrupt function programming example                       | 151 |

|    | 9.5   | List of  | registers                                                                           | 152 |

|----|-------|----------|-------------------------------------------------------------------------------------|-----|

|    | 9.6   | Registe  | er description                                                                      | 153 |

|    |       | 9.6.1    | GPIOx_DIR GPIO I/O direction register ( x =A, B, C, F )                             | 153 |

|    |       | 9.6.2    | GPIOx_OPENDRAIN GPIO output mode register ( x =A, B, C, F )                         | 153 |

|    |       | 9.6.3    | GPIOx_PDR GPIO Pull-down resistor register ( x =A, B, C, F )                        | 154 |

|    |       | 9.6.4    | GPIOx_PUR GPIO Pull-up resistor register ( x =A, B, C, F )                          | 154 |

|    |       | 9.6.5    | GPIOx_AFRH GPIO Multiplexing function register high segment ( x =A, B, C, F )       | 155 |

|    |       | 9.6.6    | GPIOx_AFRL GPIO Multiplexing function register low segment ( x =A, B, C, F )        | 155 |

|    |       | 9.6.7    | GPIOx_ANALOG GPIO Analog Digital Configuration Register ( x =A, B, C, F )           | 155 |

|    |       | 9.6.8    | GPIOx_RISEIE GPIO Rising edge interrupt enable register ( x =A, B, C, F )           | 156 |

|    |       | 9.6.9    | GPIOx_FALLIE GPIO Falling edge interrupt enable register ( x =A, B, C, F )          | 156 |

|    |       | 9.6.10   | GPIOx_ISR GPIO Interrupt flag register ( x =A, B, C, F )                            | 156 |

|    |       | 9.6.11   | GPIOx_ICR GPIO Interrupt flag clear register ( x =A, B, C, F )                      | 157 |

|    |       | 9.6.12   | GPIOx_FILTER GPIO Interrupt digital filter configuration register ( x =A, B, C, F ) | 157 |

|    |       | 9.6.13   | GPIOx_IDR GPIO input data register ( x =A, B, C, F )                                | 158 |

|    |       | 9.6.14   | GPIOx_ODR GPIO output data register ( x =A, B, C, F )                               | 158 |

|    |       | 9.6.15   | GPIOx_BRR GPIO port bit set clear register ( x =A, B, C, F )                        | 158 |

|    |       | 9.6.16   | GPIOx_BSRR GPIO port bit-setting clear register ( x =A, B, C, F )                   | 159 |

|    |       | 9.6.17   | GPIOx_TOG GPIO Port Bit Flip Register ( x =A, B, C, F )                             | 159 |

| 10 | Cycli | c redun  | dancy check (CRC)                                                                   | 160 |

|    | 10.1  | Overvi   | ew                                                                                  | 160 |

|    | 10.2  | Main fe  | eatures                                                                             | 160 |

|    | 10.3  | Function | onal description                                                                    | 161 |

|    |       | 10.3.1   | Algorithmic modes                                                                   | 161 |

|    |       | 10.3.2   | Input data bit width                                                                | 163 |

|    | 10.4  |          | mming examples                                                                      |     |

|    |       | 10.4.1   | CRC16_CCITT algorithm mode                                                          | 164 |

|    | 10.5  | List of  | registers                                                                           | 165 |

|    | 10.6  |          | er descriptions                                                                     |     |

|    |       | 10.6.1   | CRC_CR control register                                                             |     |

|    |       | 10.6.2   | CRC_DR data register                                                                |     |

|    |       | 10.6.3   | CRC_RESULT register                                                                 |     |

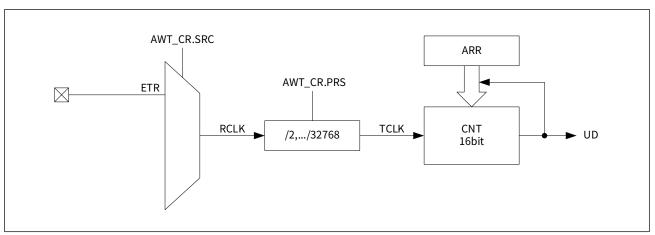

| 11 | Auto  | matic w  | vake-up timer (AWT)                                                                 |     |

|    | 11.1  |          | ew                                                                                  |     |

|    | 11.2  |          | eatures                                                                             |     |

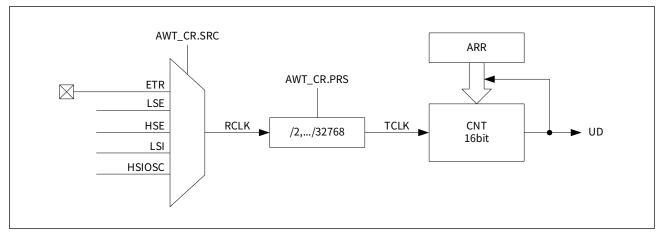

|    | 11.3  |          | onal description                                                                    |     |

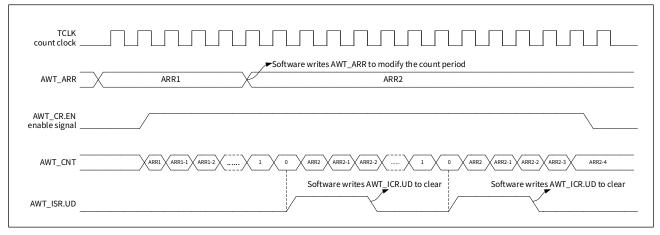

|    |       | 11.3.1   | Functional block diagram                                                            |     |

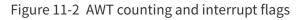

|    |       | 11.3.2   | Timing function                                                                     |     |

|    |       |          |                                                                                     |     |

|    |        | 11.3.3    | Count function                               |     |  |  |  |  |

|----|--------|-----------|----------------------------------------------|-----|--|--|--|--|

|    | 11.4   | Low po    | ower mode                                    | 173 |  |  |  |  |

|    | 11.5   | AWT in    | terrupts                                     | 173 |  |  |  |  |

|    | 11.6   | Debugg    | ebugging support                             |     |  |  |  |  |

|    | 11.7   | List of r | ist of registers                             |     |  |  |  |  |

|    | 11.8   | Registe   | Register descriptions                        |     |  |  |  |  |

|    |        | 11.8.1    | AWT_CR control register                      |     |  |  |  |  |

|    |        | 11.8.2    | AWT_ARR reload value register                |     |  |  |  |  |

|    |        | 11.8.3    | AWT_CNT count value register                 |     |  |  |  |  |

|    |        | 11.8.4    | AWT_IER interrupt enable register            |     |  |  |  |  |

|    |        | 11.8.5    | AWT_ISR interrupt flag register              |     |  |  |  |  |

|    |        | 11.8.6    | AWT_ICR interrupt flag clear register        |     |  |  |  |  |

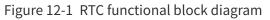

| 12 | Real t | ime clo   | ck (RTC)                                     | 178 |  |  |  |  |

|    | 12.1   | Overvie   | ew                                           | 178 |  |  |  |  |

|    | 12.2   | Main fe   | atures                                       | 178 |  |  |  |  |

|    | 12.3   | Functio   | onal description                             |     |  |  |  |  |

|    |        | 12.3.1    | •<br>Functional block diagram                |     |  |  |  |  |

|    |        | 12.3.2    | Functional overview                          |     |  |  |  |  |

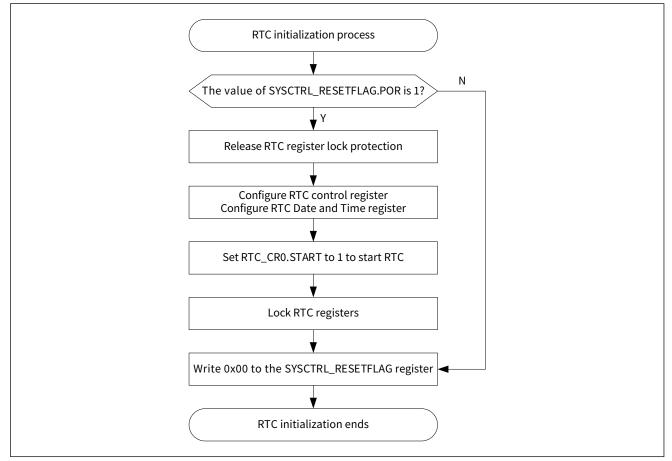

|    |        | 12.3.3    | RTC initialization settings                  |     |  |  |  |  |

|    |        | 12.3.4    | Register lock function                       |     |  |  |  |  |

|    |        | 12.3.5    | Register access operations                   |     |  |  |  |  |

|    |        | 12.3.6    | RTCOUT output                                |     |  |  |  |  |

|    |        | 12.3.7    | 1Hz signal output                            |     |  |  |  |  |

|    |        | 12.3.8    | Clock error compensation                     |     |  |  |  |  |

|    |        | 12.3.9    | Alarm clock A and alarm clock B              |     |  |  |  |  |

|    |        | 12.3.10   | Period interrupt function                    |     |  |  |  |  |

|    |        | 12.3.11   | Automatic wake-up function                   |     |  |  |  |  |

|    |        | 12.3.12   | Timestamp function                           |     |  |  |  |  |

|    |        | 12.3.13   | RTC Interrupts                               |     |  |  |  |  |

|    | 12.4   | List of r | registers                                    |     |  |  |  |  |

|    | 12.5   | Registe   | r descriptions                               | 190 |  |  |  |  |

|    |        | 12.5.1    | RTC_KEY key value register                   |     |  |  |  |  |

|    |        | 12.5.2    | RTC_CR0 control register 0                   |     |  |  |  |  |

|    |        | 12.5.3    | RTC_CR1 control register 1                   |     |  |  |  |  |

|    |        | 12.5.4    | RTC_CR2 control register 2                   |     |  |  |  |  |

|    |        | 12.5.5    | RTC_COMPEN clock error compensation register |     |  |  |  |  |

|    |        | 12.5.6    | RTC_DATE date register                       |     |  |  |  |  |

|    |        | 12.5.7    | RTC_TIME time register                       |     |  |  |  |  |

|    |       | 12.5.8    | RTC_ALARMA alarm clock A control register | 196 |

|----|-------|-----------|-------------------------------------------|-----|

|    |       | 12.5.9    | RTC_ALARMB alarm clock B control register | 197 |

|    |       | 12.5.10   | RTC_TAMPDATE timestamp date register      | 197 |

|    |       | 12.5.11   | RTC_TAMPTIME timestamp time register      | 198 |

|    |       | 12.5.12   | RTC_AWTARR wake-up timer reload value     | 198 |

|    |       | 12.5.13   | RTC_IER interrupt enable register         | 199 |

|    |       | 12.5.14   | RTC_ISR interrupt flag register           | 200 |

|    |       | 12.5.15   | RTC_ICR interrupt flag clear register     |     |

| 13 | Basic | timer (   | ВТІМ)                                     | 202 |

|    | 13.1  | Overvie   | ew                                        | 202 |

|    | 13.2  | Main fe   | eatures                                   | 202 |

|    | 13.3  | Functio   | onal description                          | 203 |

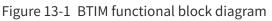

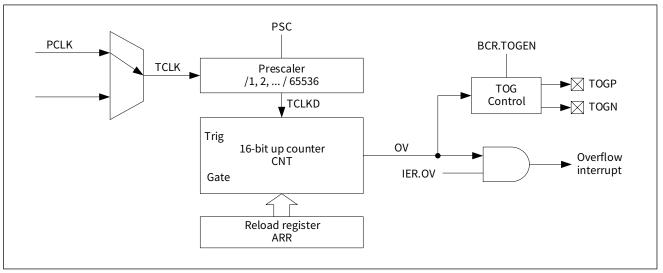

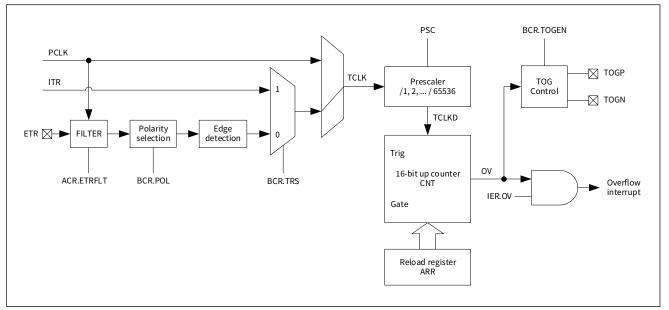

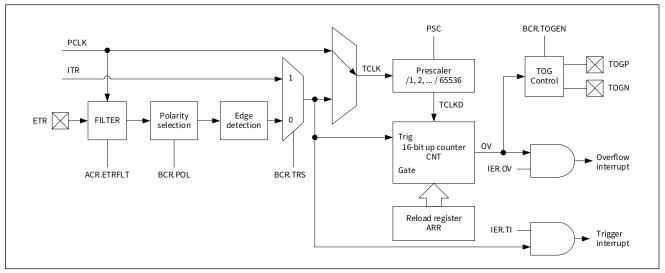

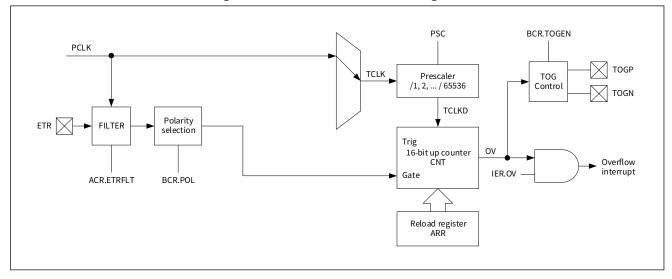

|    |       | 13.3.1    | ·<br>Functional block diagram             |     |

|    |       |           | 13.3.1.1 Filter unit                      | 203 |

|    |       |           | 13.3.1.2 Polarity selection unit          | 204 |

|    |       |           | 13.3.1.3 Edge detection unit              | 204 |

|    |       |           | 13.3.1.4 Prescaler                        | 204 |

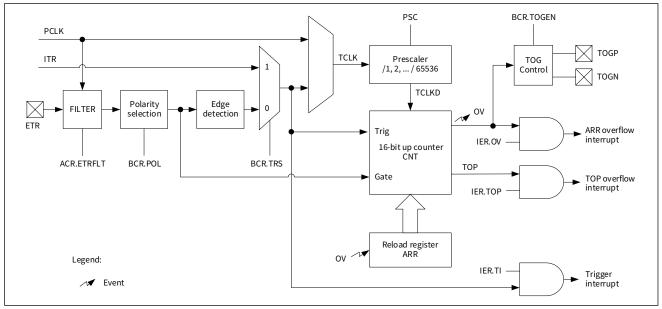

|    |       |           | 13.3.1.5 Counting unit                    | 205 |

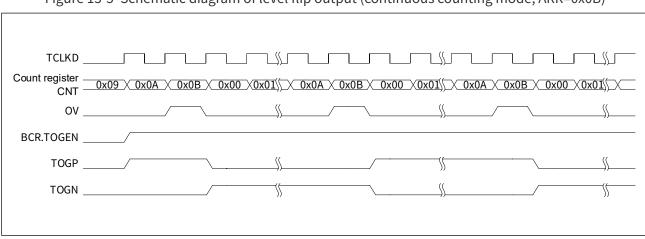

|    |       |           | 13.3.1.6 Flip output unit                 | 207 |

|    |       | 13.3.2    | Operating modes                           | 208 |

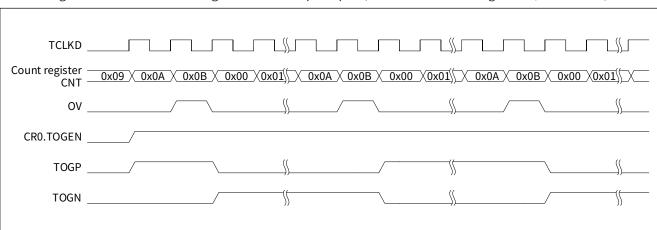

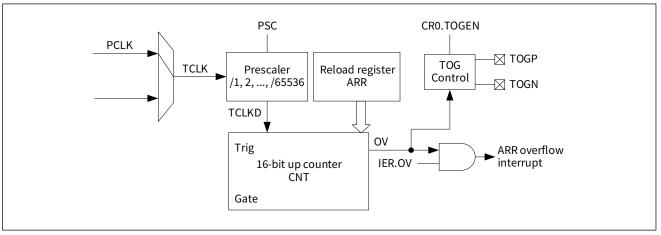

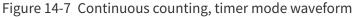

|    |       |           | 13.3.2.1 Timer mode                       | 209 |

|    |       |           | 13.3.2.2 Counter mode                     | 210 |

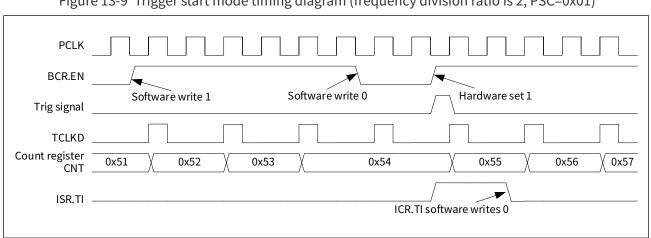

|    |       |           | 13.3.2.3 Trigger start mode               | 211 |

|    |       |           | 13.3.2.4 Gated mode                       | 212 |

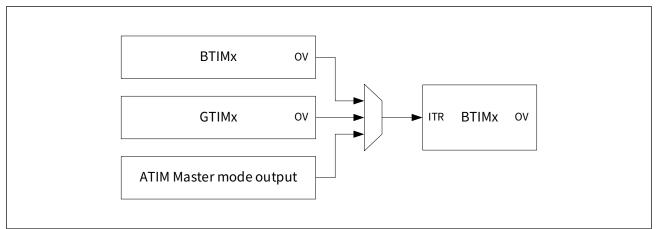

|    |       | 13.3.3    | Internal cascade ITR                      |     |

|    |       | 13.3.4    | External interconnection ETR              | 215 |

|    | 13.4  | Debug     | ging support                              | 216 |

|    | 13.5  | Progra    | mming examples                            | 217 |

|    |       | 13.5.1    | Timer mode programming example            | 217 |

|    |       | 13.5.2    | Counter mode programming examples         | 217 |

|    |       |           | 13.5.2.1 Count external ETR signals       | 217 |

|    |       |           | 13.5.2.2 Count internal ITR signals       | 218 |

|    |       | 13.5.3    | Trigger start mode programming example    | 218 |

|    |       | 13.5.4    | Gated mode programming example            | 219 |

|    | 13.6  | List of ı | registers                                 | 220 |

|    | 13.7  | Registe   | er descriptions                           | 221 |

|    |       | 13.7.1    | BTIMx_BCR basic control register          | 221 |

|    |       | 13.7.2    | BTIMx_ACR advanced control register       | 222 |

|    |      | 13.7.3   | BTIMx_PSC Prescaler register            | 222 |

|----|------|----------|-----------------------------------------|-----|

|    |      | 13.7.4   | BTIMx_ARR reload register               |     |

|    |      | 13.7.5   | BTIMx_CNT count register                |     |

|    |      | 13.7.6   | BTIMx_IER interrupt enable register     |     |

|    |      | 13.7.7   | BTIMx_ISR interrupt flag register       |     |

|    |      | 13.7.8   | BTIMx_ICR interrupt flag clear register |     |

|    |      | 13.7.9   | BTIMx_DMA DMA trigger register          |     |

| 14 | Gene | ral-purp | oose timer (GTIM)                       | 225 |

|    | 14.1 | Overvie  | ew                                      | 225 |

|    | 14.2 | Main fe  | eatures                                 |     |

|    | 14.3 |          | onal description                        |     |

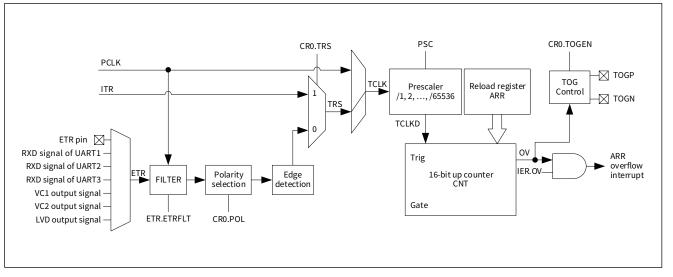

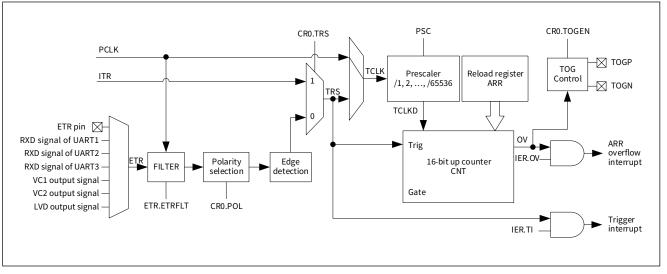

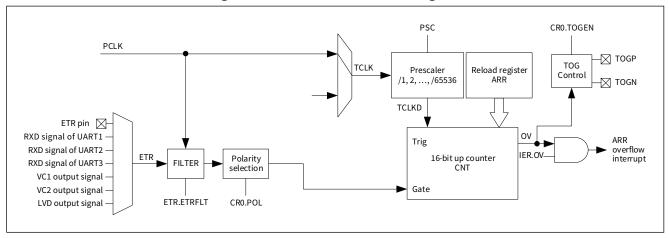

|    |      | 14.3.1   | Functional block diagram                |     |

|    |      |          | 14.3.1.1 Prescaler                      |     |

|    |      |          | 14.3.1.2 Counting unit                  |     |

|    |      |          | 14.3.1.3 Input control unit             |     |

|    |      |          | 14.3.1.4 Capture compare channel        |     |

|    |      |          | 14.3.1.5 Output control unit            |     |

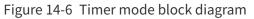

|    |      |          | 14.3.1.6 Flip output unit               |     |

|    |      | 14.3.2   | Basic operating modes                   |     |

|    |      |          | 14.3.2.1 Timer mode                     |     |

|    |      |          | 14.3.2.2 Counter mode                   |     |

|    |      |          | 14.3.2.3 Trigger start mode             |     |

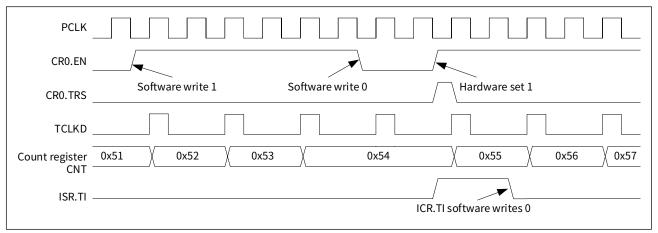

|    |      |          | 14.3.2.4 Gated mode                     |     |

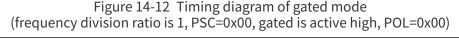

|    |      | 14.3.3   | Input capture function                  |     |

|    |      |          | 14.3.3.1 Input capture                  |     |

|    |      |          | 14.3.3.2 Input capture sources          |     |

|    |      | 14.3.4   | Output compare function                 |     |

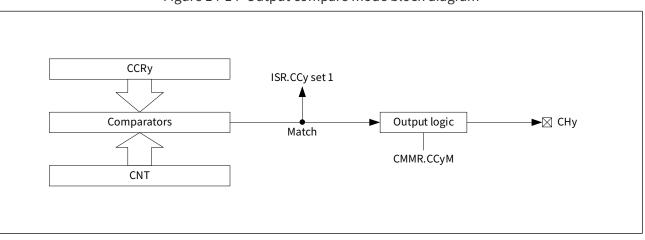

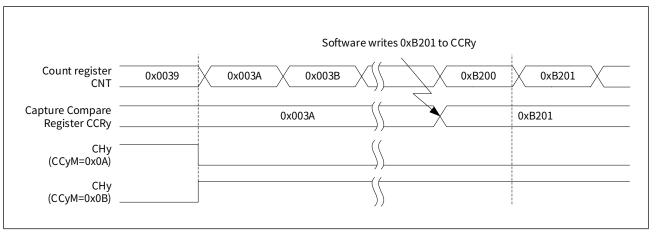

|    |      |          | 14.3.4.1 Output compare                 |     |

|    |      |          | 14.3.4.2 Force output function          |     |

|    |      |          | 14.3.4.3 PWM output function            |     |

|    |      | 14.3.5   | Encoding counting mode                  |     |

|    |      | 14.3.6   | Internal cascade ITR                    |     |

|    |      | 14.3.7   | On-chip peripheral interconnect ETR     |     |

|    | 14.4 | Debug    | ging support                            |     |

|    | 14.5 | Progra   | mming examples                          |     |

|    |      | 14.5.1   | Timer mode programming example          |     |

|    |      | 14.5.2   | Counter mode programming examples       |     |

|    |      |          | 14.5.2.1 Count external ETR signals     |     |

|    |      |          | 14.5.2.2 Count internal ITR signal      |     |

|    |      |          |                                         |     |

|    |      | 14.5.3    | Trigger start mode programming example      | 250 |

|----|------|-----------|---------------------------------------------|-----|

|    |      | 14.5.4    | Gated mode programming example              | 251 |

|    |      | 14.5.5    | Input capture programming example           | 251 |

|    |      | 14.5.6    | Output compare programming example          |     |

|    |      | 14.5.7    | PWM output programming example              |     |

|    |      | 14.5.8    | Encoder mode programming example            | 253 |

|    | 14.6 | List of I | registers                                   | 254 |

|    | 14.7 | Registe   | er descriptions                             | 255 |

|    |      | 14.7.1    | GTIMx_CR0 control register 0                | 255 |

|    |      | 14.7.2    | GTIMx_CR1 control register 1                | 257 |

|    |      | 14.7.3    | GTIMx_PSC Prescaler register                | 258 |

|    |      | 14.7.4    | GTIMx_ETR external trigger control register | 258 |

|    |      | 14.7.5    | GTIMx_CMMR compare capture control register |     |

|    |      | 14.7.6    | GTIMx_ARR reload register                   | 259 |

|    |      | 14.7.7    | GTIMx_CNT count register                    | 259 |

|    |      | 14.7.8    | GTIMx_CCR1 compare capture register 1       |     |

|    |      | 14.7.9    | GTIMx_CCR2 compare capture register 2       |     |

|    |      | 14.7.10   | GTIMx_CCR3 compare capture register 3       |     |

|    |      | 14.7.11   | GTIMx_CCR4 compare capture register 4       |     |

|    |      | 14.7.12   | GTIMx_IER interrupt enable register         |     |

|    |      | 14.7.13   | GTIMx_ISR interrupt flag register           |     |

|    |      | 14.7.14   | GTIMx_ICR interrupt flag clear register     |     |

|    |      | 14.7.15   | GTIMx_DMA DMA trigger register              |     |

| 15 | Adva | nced-co   | ontrol timer (ATIM)                         | 265 |

|    | 15.1 | Overvi    | ew                                          | 265 |

|    | 15.2 | Main fe   | eatures                                     | 265 |

|    | 15.3 | Functio   | onal description                            | 266 |

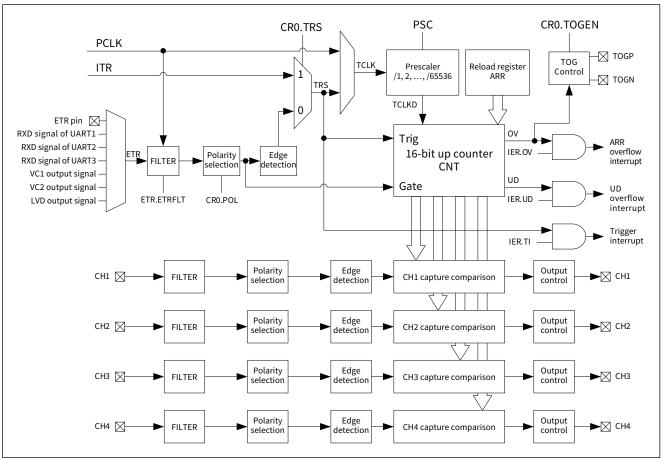

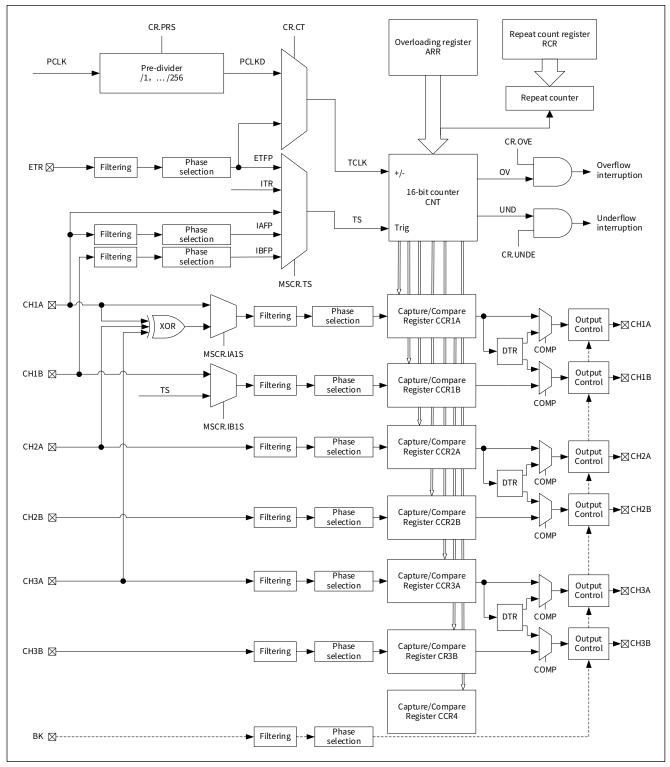

|    |      | 15.3.1    | Functional block diagram                    |     |

|    |      |           | 15.3.1.1 Clock sources selection            |     |

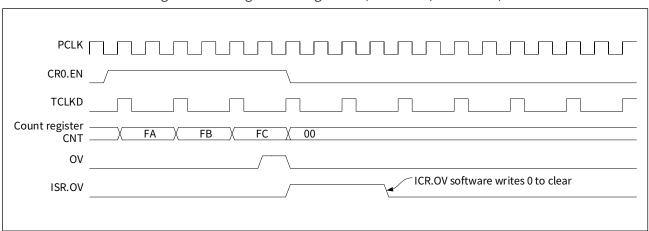

|    |      |           | 15.3.1.2 Update Event (UEV)                 |     |

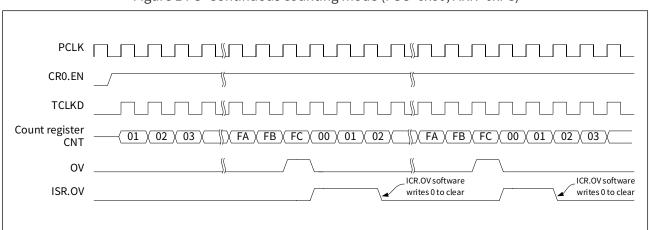

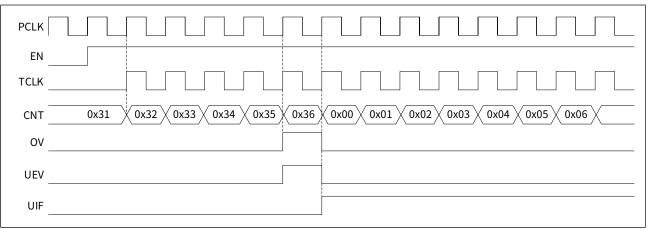

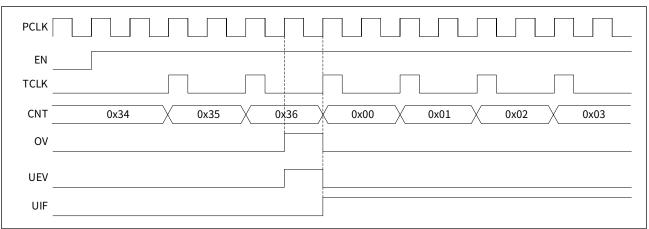

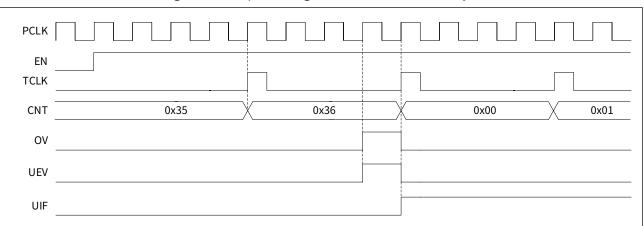

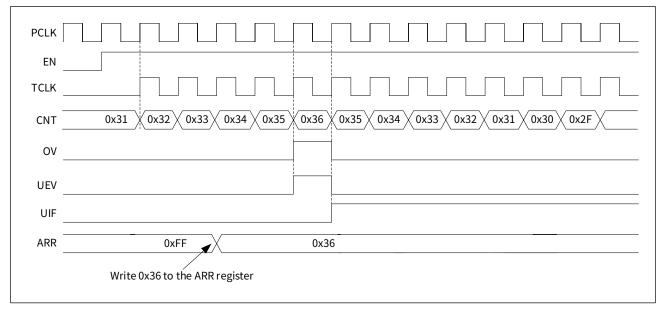

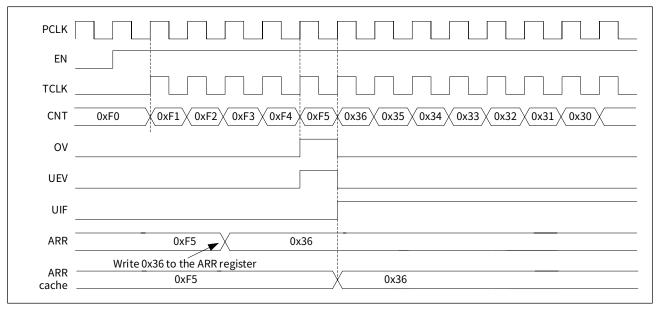

|    |      |           | 15.3.1.3 Counting modes                     |     |

|    |      |           | 15.3.1.4 Reload register                    |     |

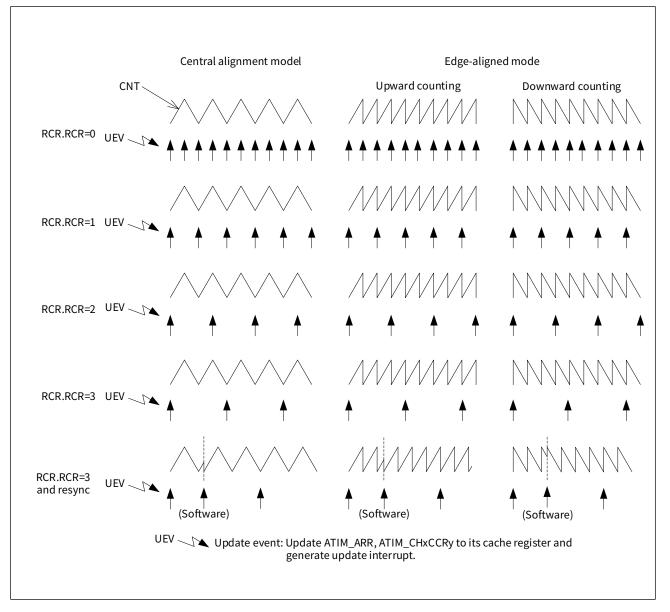

|    |      |           | 15.3.1.5 Repetition counter                 | 275 |

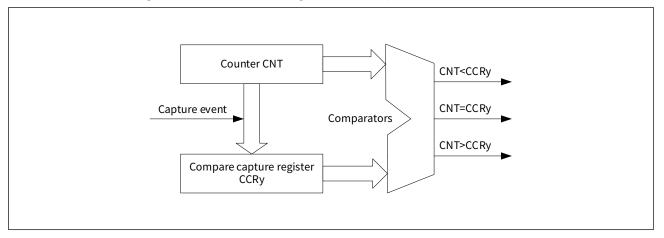

|    |      |           | 15.3.1.6 Compare/capture channels           |     |

|    |      | 15.3.2    | Input capture mode                          | 278 |

|    |      |           | 15.3.2.1 Input capture                      | 278 |

|    |      |           | 15.3.2.2 PWM input mode                     | 279 |

|    |      |           | 15.3.2.3 Input capture trigger source       |     |

|    |      | 15.3.3    | Output compare function                     |     |

| 15.3.3.2       Forced output       282         15.3.3.3       Single pulse mode       283         15.3.3.4       Independent PWM output       284         15.3.3.5       Complementary PWM output and dead-time insertion       290         15.3.4.5       Brake function       291         15.3.5       Force function       291         15.3.6       Brake function       292         15.3.7       Compare match interrupt       292         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       298         15.3.7.2       Rest function (slave mode)       299         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7       Guadrature encoding mode (slave mode)       299         15.3.7       Guadrature encoding mode (slave mode)       299         15.3.8       Internal cascade ITR       300         15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15.3.3.3       Single pulse mode       283         15.3.3.4       Independent PWM output       284         15.3.3.5       Complementary PWM output and dead-time insertion       290         15.3.6       Brake function       291         15.3.7       Compare match interrupt       292         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Use mode       297         15.3.7.1       Use internal clock (master mode)       299         15.3.7.2       Reset function (slave mode)       299         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.8       Internal cascade ITR       300         15.4       Debugging support       303         15.5.1       Input capture       303         15.5.2       PVM input       303         15.5.3       Output compare function       304         15.5.4       <                                                                |      |                                                                                                                                                                              | 15.3.3.1 Output compare                                                                                                                                                                                                                                                                                                                                 |             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

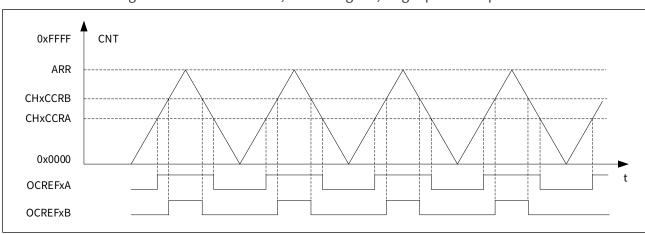

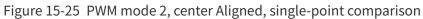

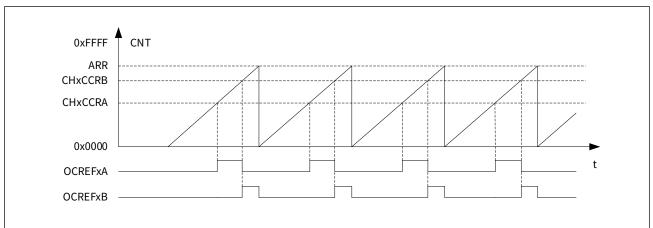

| 15.3.3.4       Independent PWM output       284         15.3.3.5       Complementary PWM output and dead-time insertion       290         15.3.3.6       Brake function       291         15.3.3.7       Compare match interrupt       292         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       298         15.3.7.2       Reset function (slave mode)       299         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.8       Internal cascade ITR       300         15.3.9       On-chip peripheral interconnect ETR       301         15.4       Debugging support       303         15.5.1       Input capture       303         15.5.2       PVM input       303         15.5.4       Complementary PWM output       304         15.5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15.3.3.4       Independent PWM output       284         15.3.3.5       Complementary PWM output and dead-time insertion       290         15.3.3.6       Brake function       291         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       DMA function       296         15.3.7       Slave mode       297         15.3.7       Slave mode       298         15.3.7.1       Use internal clock (master mode)       299         15.3.7.2       Reset function (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.8       Internal cascade ITR       300         15.4       Debugging support       303         15.5.1       Input capture       303         15.5.2       PVM input       304         15.5.4       Complementary PWM output       304         15.5.5                                                                           |      |                                                                                                                                                                              | 15.3.3.2 Forced output                                                                                                                                                                                                                                                                                                                                  |             |

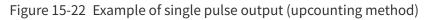

| 15.3.3.5       Complementary PWM output and dead-time insertion       290         15.3.3.6       Brake function       291         15.3.3.7       Compare match interrupt.       292         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Tisger ADC       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       299         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.8       Internal cascade ITR       300         15.4       Debugging support       302         15.5       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.4       Complementary PWM output       303         15.5.5       DMA function       304         15.5.6       Trigger mode       307                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15.3.3.5       Complementary PWM output and dead-time insertion       290         15.3.3.6       Brake function       291         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Compare match interrupt       292         15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       298         15.3.7.2       Reset function (slave mode)       299         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.8       Internal cascade ITR       300         15.4       Debugging support       302         15.5       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.4       Complementary PWM output       304         15.5.5       Trigger mode <td></td> <td></td> <td>15.3.3.3 Single pulse mode</td> <td> 283</td> |      |                                                                                                                                                                              | 15.3.3.3 Single pulse mode                                                                                                                                                                                                                                                                                                                              | 283         |

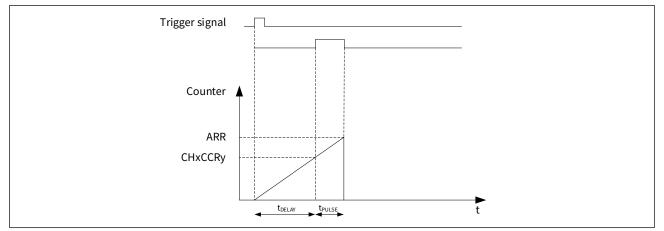

| 15.3.3.6       Brake function       291         15.3.3.7       Compare match interrupt.       292         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7       Slave mode       297         15.3.7       Slave mode       297         15.3.7       Ise internal clock (master mode)       298         15.3.7.1       Use internal clock (mode)       299         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7       Quadrature encoding mode (slave mode)       299         15.3.8       Internal cascade ITR       300         15.4       Debugging support       302         15.5       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.3       Output compare function       304         15.5.4       Complementary PWM output       304         15.5.5       DMA function       305         15.5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15.3.3.6       Brake function       291         15.3.3.7       Compare match interrupt.       292         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Slave mode.       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       298         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7       Quadrature encoding mode (slave mode)       299         15.3.7       Quadrature encoding mode (slave mode)       299         15.3.7       Pobugging support       300         15.4       Debugging support       302         15.5       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       304         15.5.4       Complementary PVM output       304         15.5.5       <                                                                |      |                                                                                                                                                                              | 15.3.3.4 Independent PWM output                                                                                                                                                                                                                                                                                                                         |             |

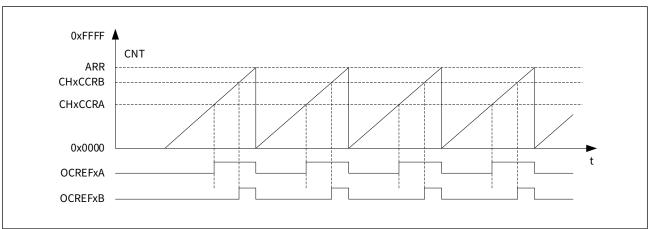

| 15.3.3.7       Compare match interrupt.       292         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC.       296         15.3.6       DMA function       296         15.3.7       Slave mode.       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       298         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.8       Internal cascade ITR       300         15.3.9       On-chip peripheral interconnect ETR       301         15.4       Debugging support       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.4       Complementary PWM output       304         15.5.5       DMA function       305         15.5.6       Trigger mode       306         15.5.7       Gated Mode       307         15.5.8       Internal cascade ITR       309 <td>15.3.3.7       Compare match interrupt.       292         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC.       296         15.3.6       DMA function.       296         15.3.7       Slave mode.       297         15.3.7.1       Use internal clock (master mode).       298         15.3.7.2       Reset function (slave mode).       299         15.3.7.3       Trigger mode (slave mode).       299         15.3.7.4       External clock mode (slave mode).       299         15.3.7.5       Quadrature encoding mode (slave mode).       299         15.3.7.6       Gated function (slave mode).       299         15.3.8       Internal cascade ITR.       300         15.3.9       On-chip peripheral interconnect ETR       301         15.4       Debugging support       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.4       Complementary PWM output       304         15.5.5       DMA function.       305         15.5.6       Trigger mode.       307         15.5.8       Internal cascade ITR.       307         15.5.8       Internal cascade ITR.</td> <td></td> <td></td> <td>15.3.3.5 Complementary PWM output and dead-time insertion</td> <td> 290</td>                              | 15.3.3.7       Compare match interrupt.       292         15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC.       296         15.3.6       DMA function.       296         15.3.7       Slave mode.       297         15.3.7.1       Use internal clock (master mode).       298         15.3.7.2       Reset function (slave mode).       299         15.3.7.3       Trigger mode (slave mode).       299         15.3.7.4       External clock mode (slave mode).       299         15.3.7.5       Quadrature encoding mode (slave mode).       299         15.3.7.6       Gated function (slave mode).       299         15.3.8       Internal cascade ITR.       300         15.3.9       On-chip peripheral interconnect ETR       301         15.4       Debugging support       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.4       Complementary PWM output       304         15.5.5       DMA function.       305         15.5.6       Trigger mode.       307         15.5.8       Internal cascade ITR.       307         15.5.8       Internal cascade ITR.                                                                    |      |                                                                                                                                                                              | 15.3.3.5 Complementary PWM output and dead-time insertion                                                                                                                                                                                                                                                                                               | 290         |

| 15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       298         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.8       Internal cascade ITR       300         15.3.9       On-chip peripheral interconnect ETR       301         15.4       Debugging support       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.3       Output compare function       304         15.5.4       Complementary PWM output       304         15.5.5       DMA function       305         15.5.6       Trigger mode       306         15.5.7       Gated Mode       307         15.5.8       Internal cascade ITR       307                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15.3.4       Quadrature encoding counting       294         15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       298         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.8       Internal cascade ITR       300         15.4       Debugging support       302         15.5       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       304         15.5.4       Complementary PWM output       304         15.5.5       DMA function       305         15.5.6       Trigger mode       307         15.5.6       Trigger mode       307         15.5.7       Gated Mode       307         15.5.8       Internal cascade ITR       309         1                                                                                                       |      |                                                                                                                                                                              | 15.3.3.6 Brake function                                                                                                                                                                                                                                                                                                                                 | 291         |

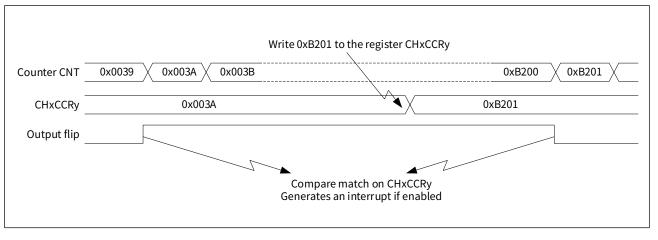

| 15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       298         15.3.7.2       Reset function (slave mode)       299         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.8       Internal cascade ITR       300         15.5       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       304         15.5.4       Complementary PWM output       304                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15.3.5       Trigger ADC       296         15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       298         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7       Ou-chip peripheral interconnect ETR       301         15.4       Debugging support       302         15.5       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.3       Output compare function       304         15.5.4       Complementary PWM output       304         15.5.5       DMA function       305         15.5.6       Trigger mode                                                                    |      |                                                                                                                                                                              | 15.3.3.7 Compare match interrupt                                                                                                                                                                                                                                                                                                                        | 292         |

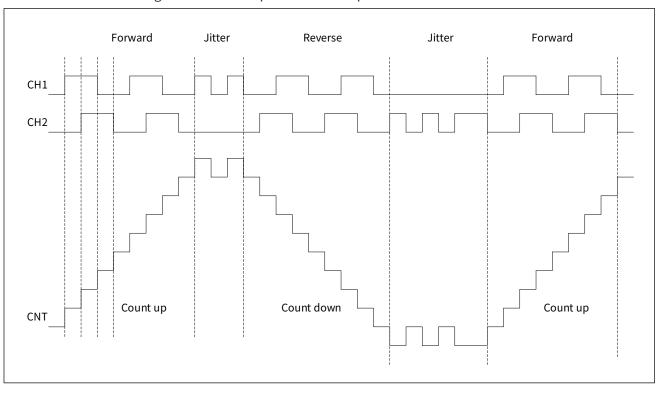

| 15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       298         15.3.7.2       Reset function (slave mode)       299         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7       Gated function (slave mode)       299         15.3.7       Debugging support       302         15.4       Debugging support       302         15.5.1       Input capture       303         15.5.2       PWM input       303 </td <td>15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       298         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7       Gated function (slave mode)       299         15.3.7       Debugging support       302         15.7       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       303</td> <td></td> <td>15.3.4</td> <td>Quadrature encoding counting</td> <td></td> | 15.3.6       DMA function       296         15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       298         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7       Gated function (slave mode)       299         15.3.7       Debugging support       302         15.7       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       303                                                              |      | 15.3.4                                                                                                                                                                       | Quadrature encoding counting                                                                                                                                                                                                                                                                                                                            |             |

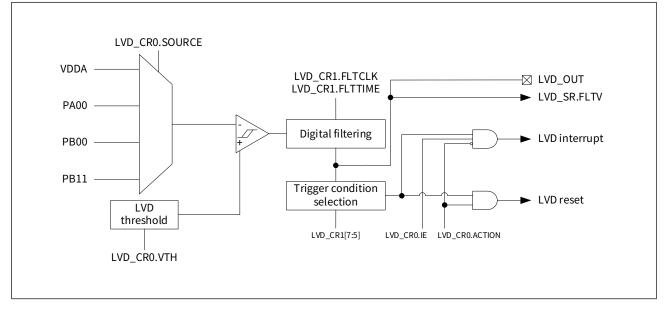

| 15.3.7       Slave mode.       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       298         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.8       Internal cascade ITR       300         15.9       On-chip peripheral interconnect ETR       301         15.4       Debugging support       302         15.5       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.3       Output compare function       304         15.5.4       Complementary PWM output       304         15.5.5       DMA function       305         15.5.6       Trigger mode       307         15.5.8       Internal cascade ITR       307         15.5.8       Internal cascade ITR       307         15.5.8       Internal cascade ITR </td <td>15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       298         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.8       Internal cascade ITR       300         15.4       Debugging support       302         15.5       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.3       Output compare function       304         15.5.4       Complementary PWM output       304         15.5.5       DMA function       305         15.5.6       Trigger mode       307         15.5.8       Internal cascade ITR       307         15.5.8       Internal cascade ITR       307         15.5.8       Internal cascade ITR       307         15.5.8       Internal cascade ITR</td> <td></td> <td>15.3.5</td> <td>Trigger ADC</td> <td> 296</td>                                                                       | 15.3.7       Slave mode       297         15.3.7.1       Use internal clock (master mode)       297         15.3.7.2       Reset function (slave mode)       298         15.3.7.3       Trigger mode (slave mode)       299         15.3.7.4       External clock mode (slave mode)       299         15.3.7.5       Quadrature encoding mode (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.7.6       Gated function (slave mode)       299         15.3.8       Internal cascade ITR       300         15.4       Debugging support       302         15.5       Programming examples       303         15.5.1       Input capture       303         15.5.2       PWM input       303         15.5.3       Output compare function       304         15.5.4       Complementary PWM output       304         15.5.5       DMA function       305         15.5.6       Trigger mode       307         15.5.8       Internal cascade ITR                                                                                    |      | 15.3.5                                                                                                                                                                       | Trigger ADC                                                                                                                                                                                                                                                                                                                                             | 296         |